Design & specifications#

If you want to know how BeagleV-Ahead board is designed and what are its high-level specifications then this chapter is for you. We are going to discuss each hardware design element in detail and provide high-level device specifications in a short and crisp form as well.

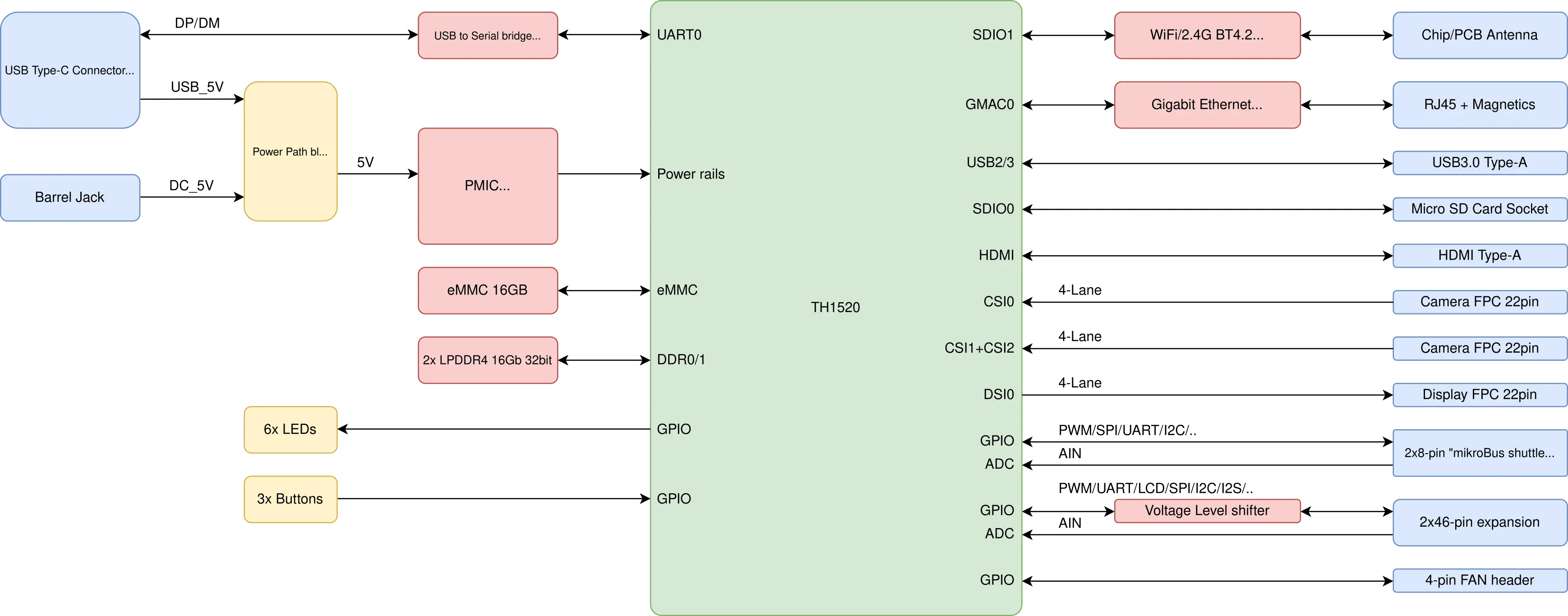

Block diagram#

Fig. 512 System block diagram#

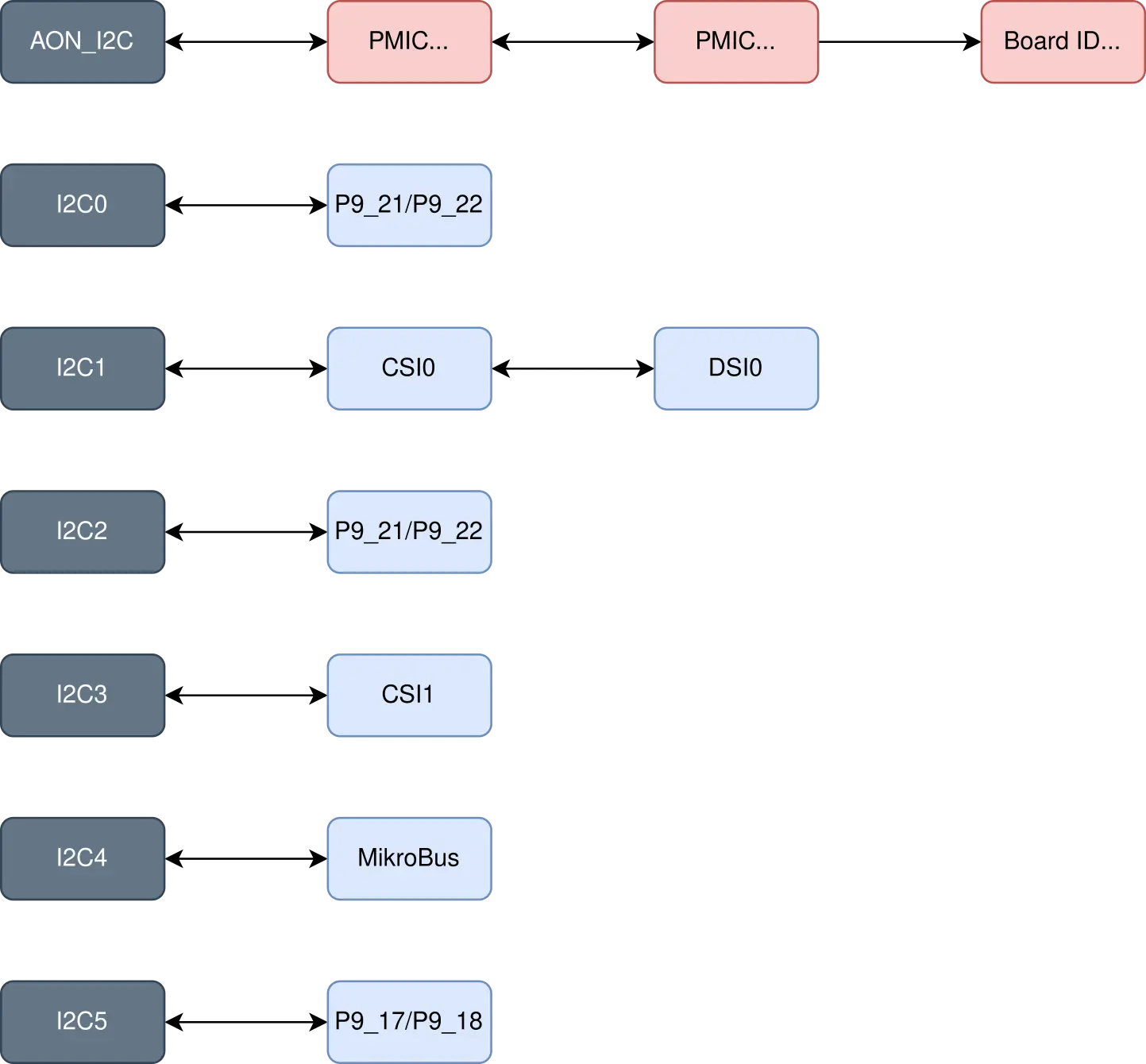

Fig. 513 I2C-Usage diagram#

System on Chip (SoC)#

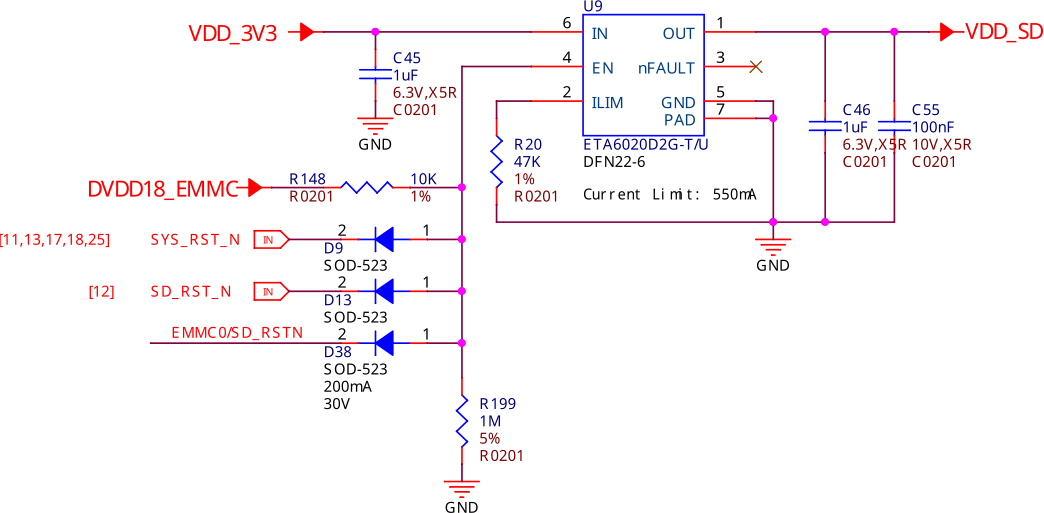

Fig. 514 SoC eMMC power switch#

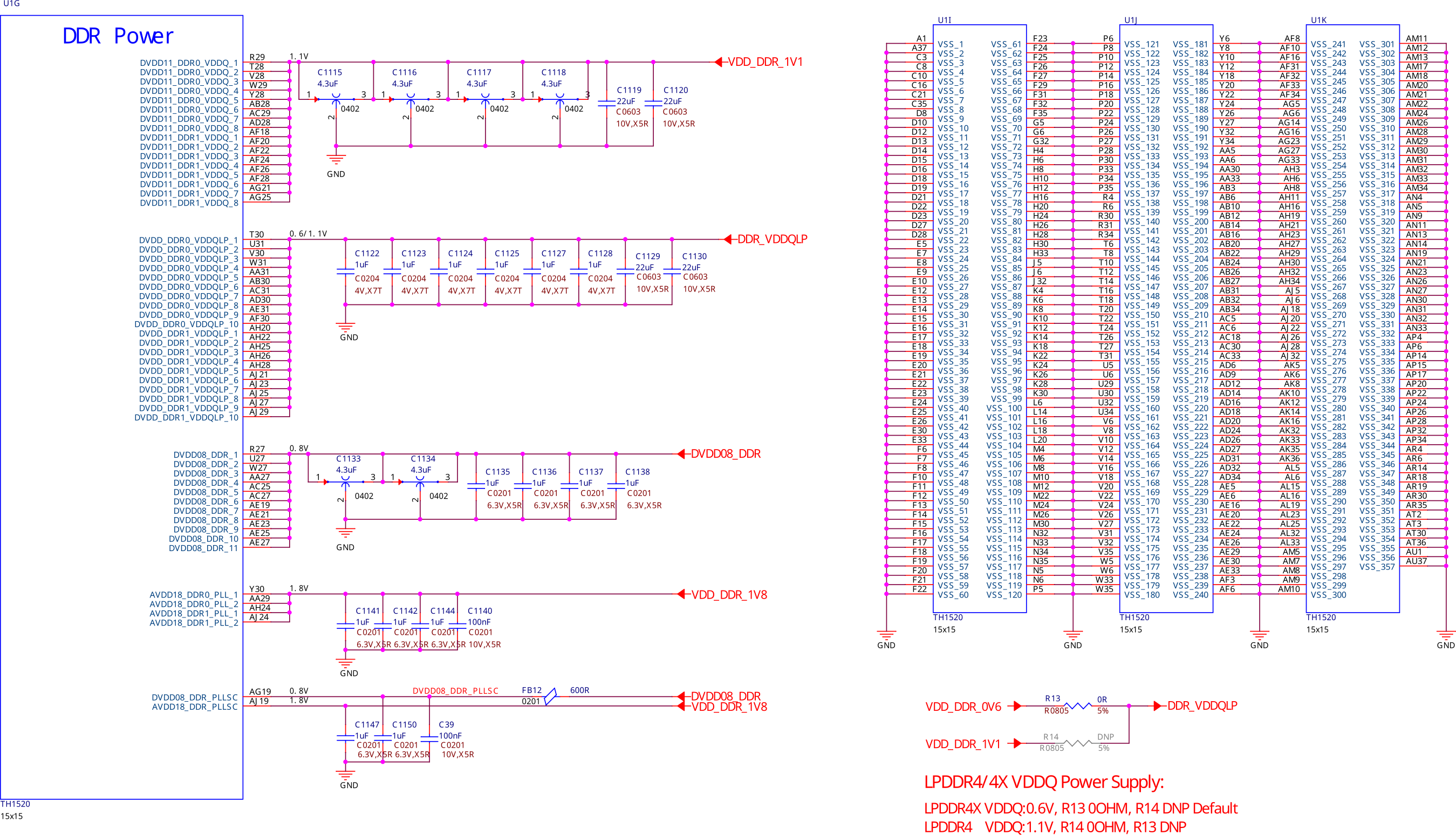

Fig. 515 SoC DDR Power#

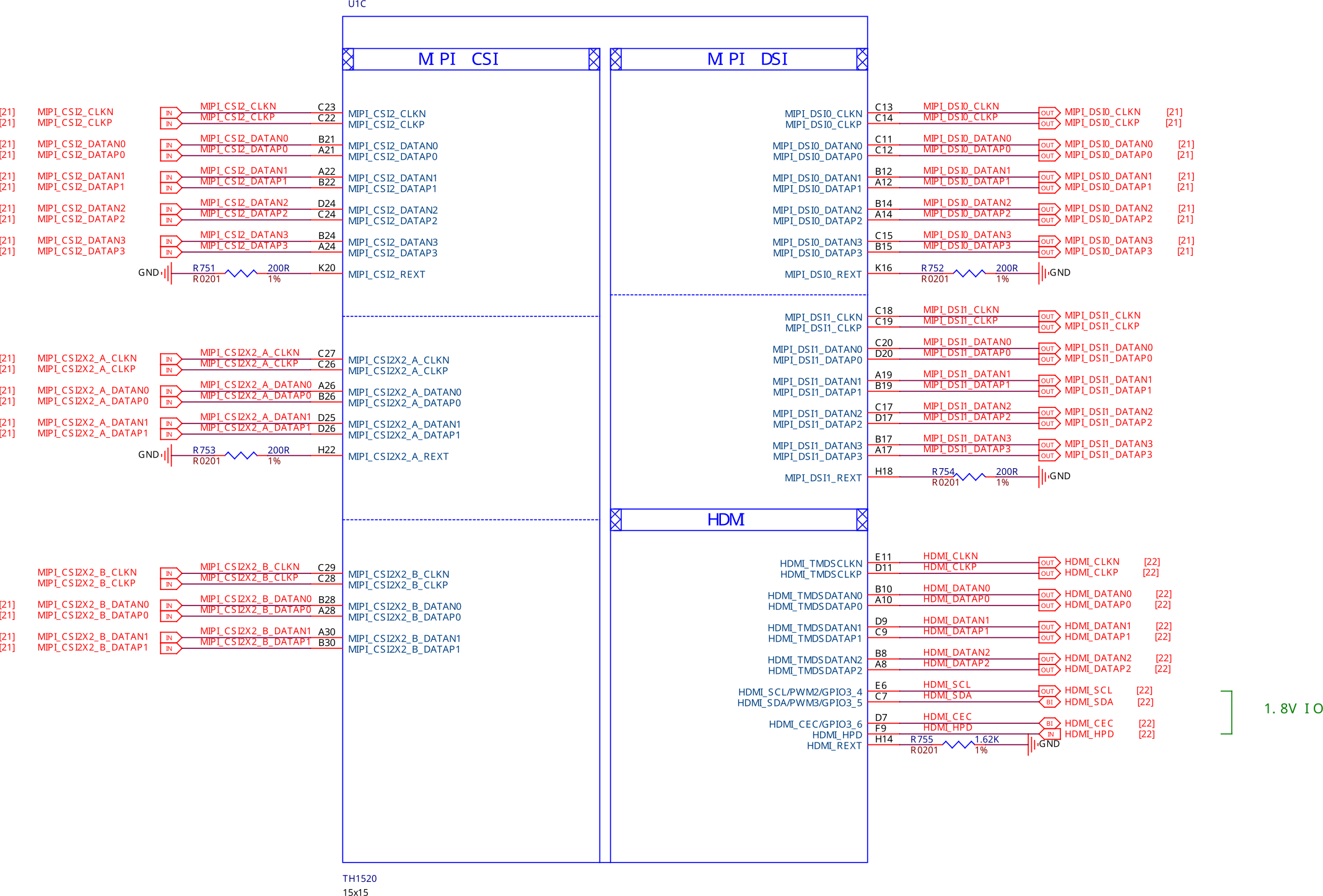

Fig. 516 SoC MIPI CSI DSI HDMI#

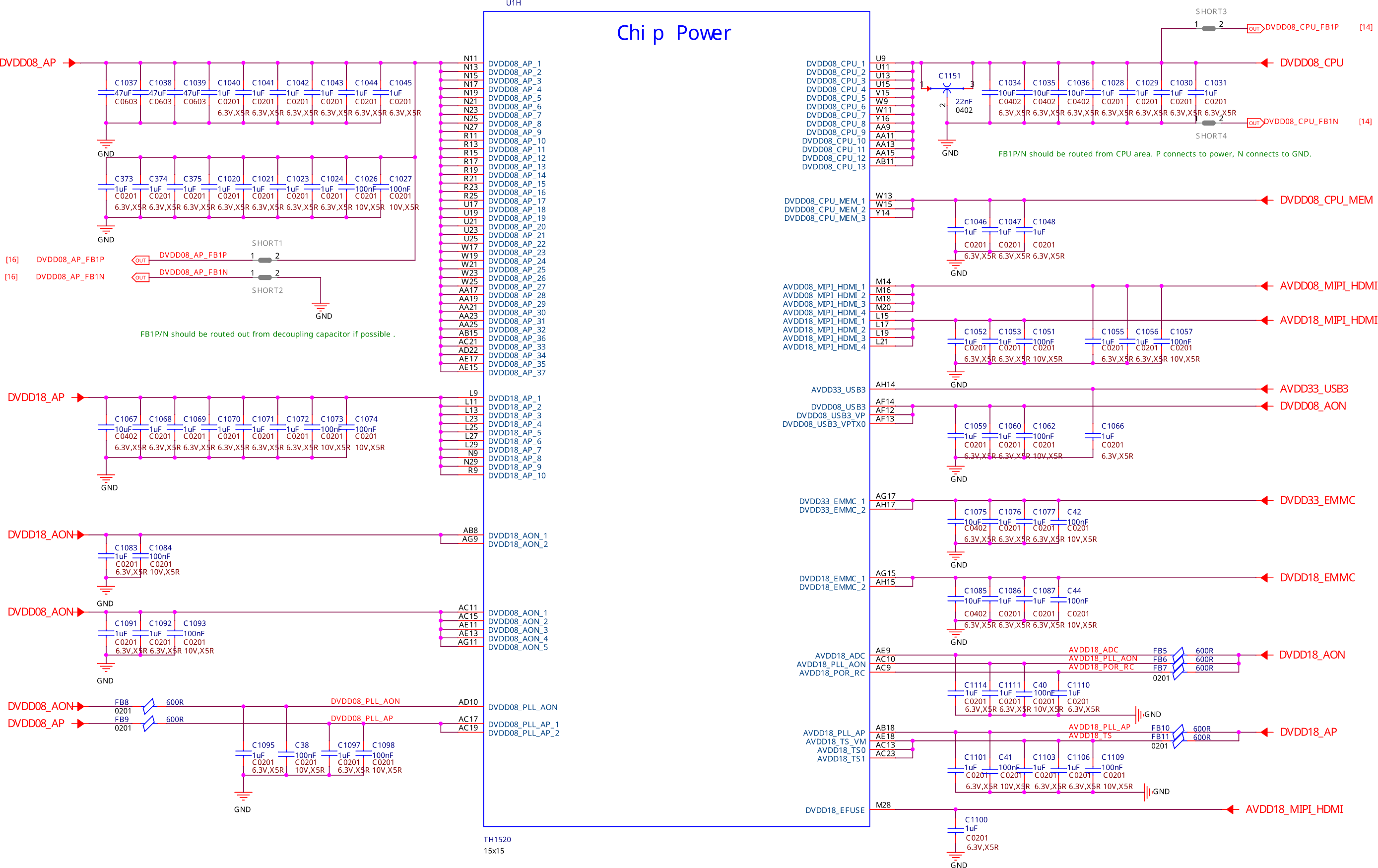

Fig. 517 SoC power#

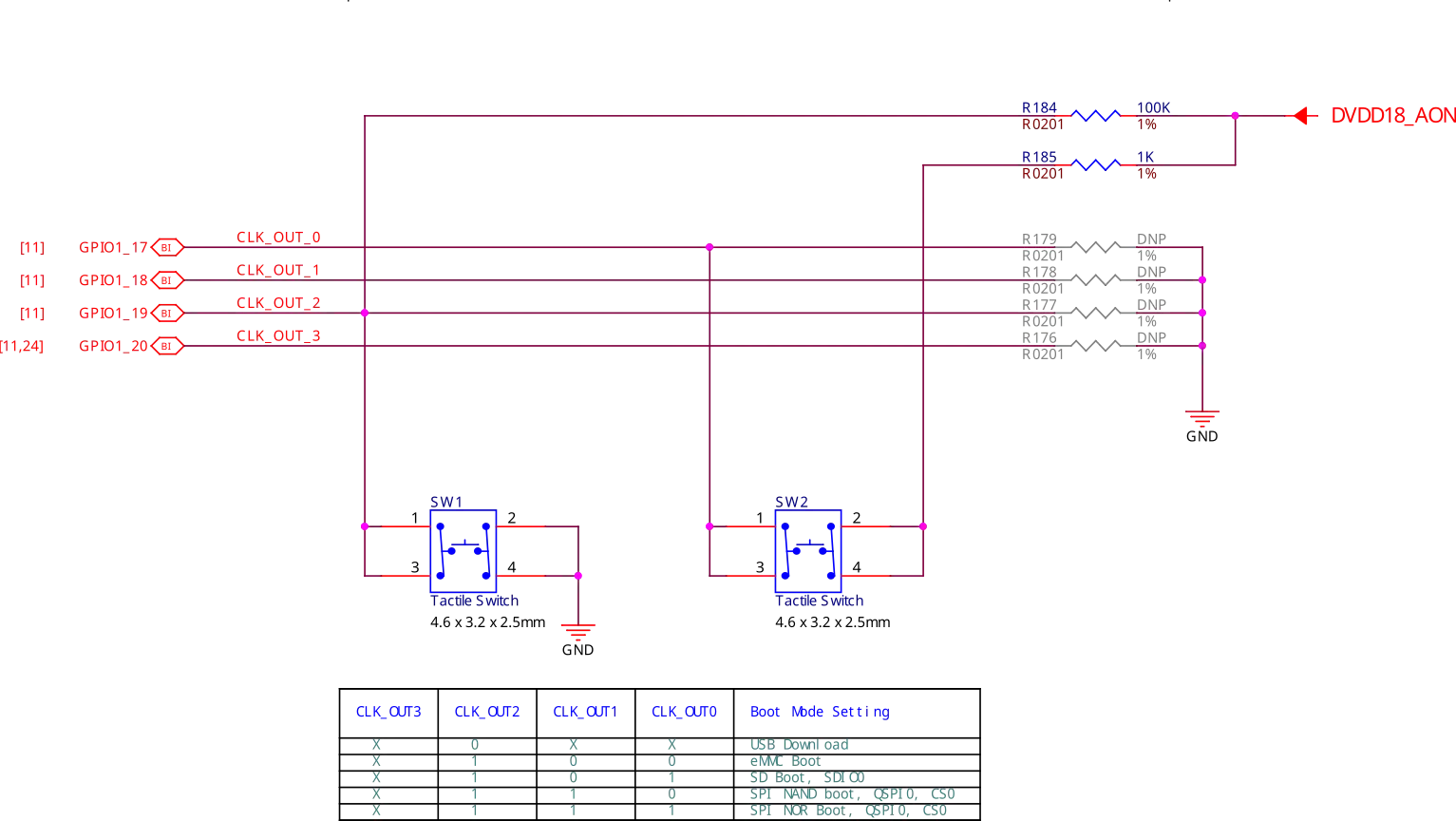

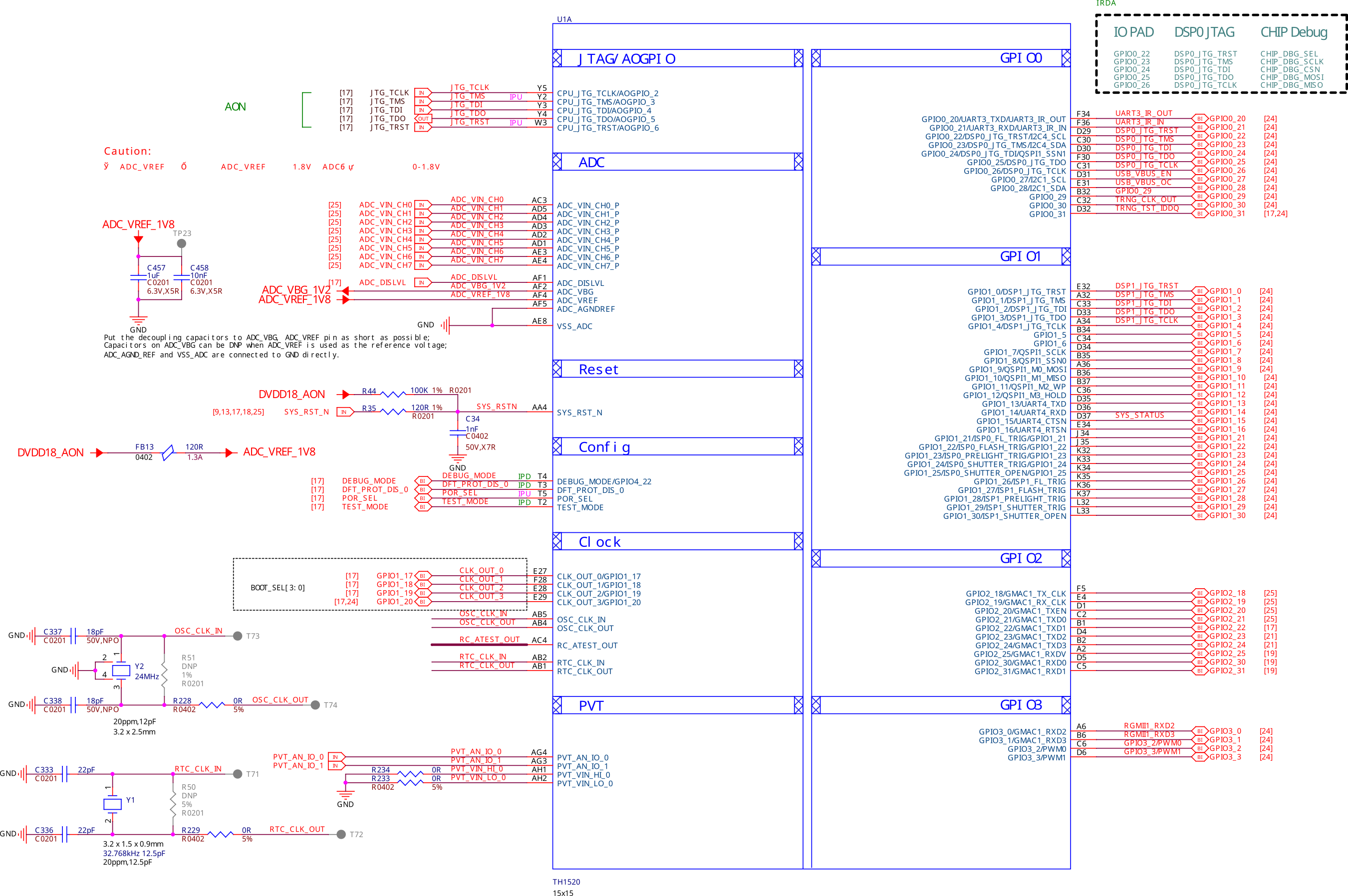

Fig. 518 SoC sys, ADC, and Clock#

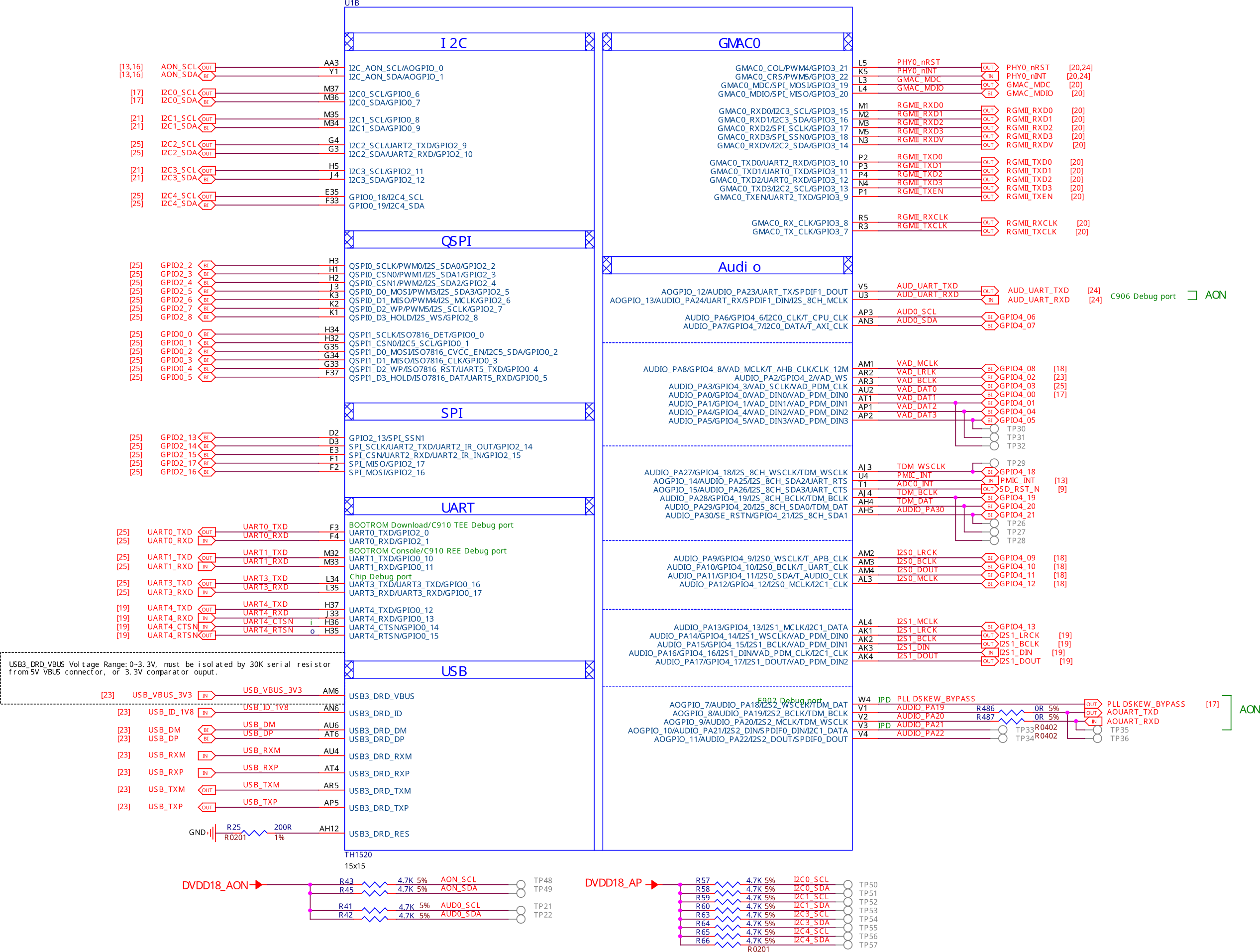

Fig. 519 SoC USB GMAC Audio#

Power management#

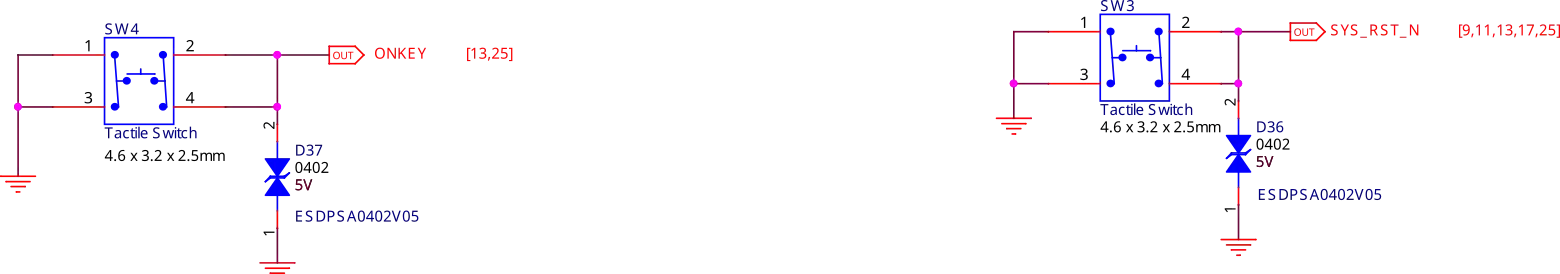

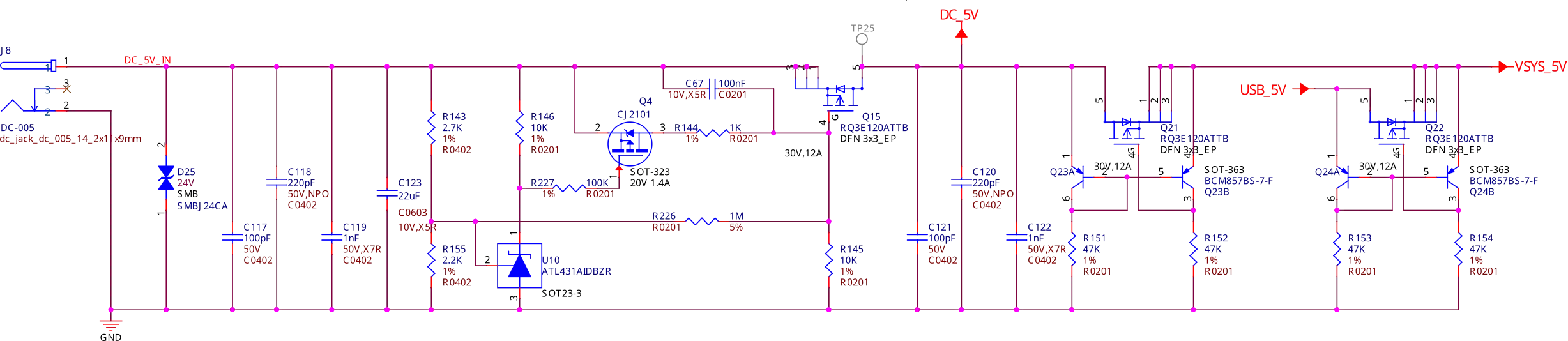

Barrel jack#

Fig. 520 Barrel jack power input#

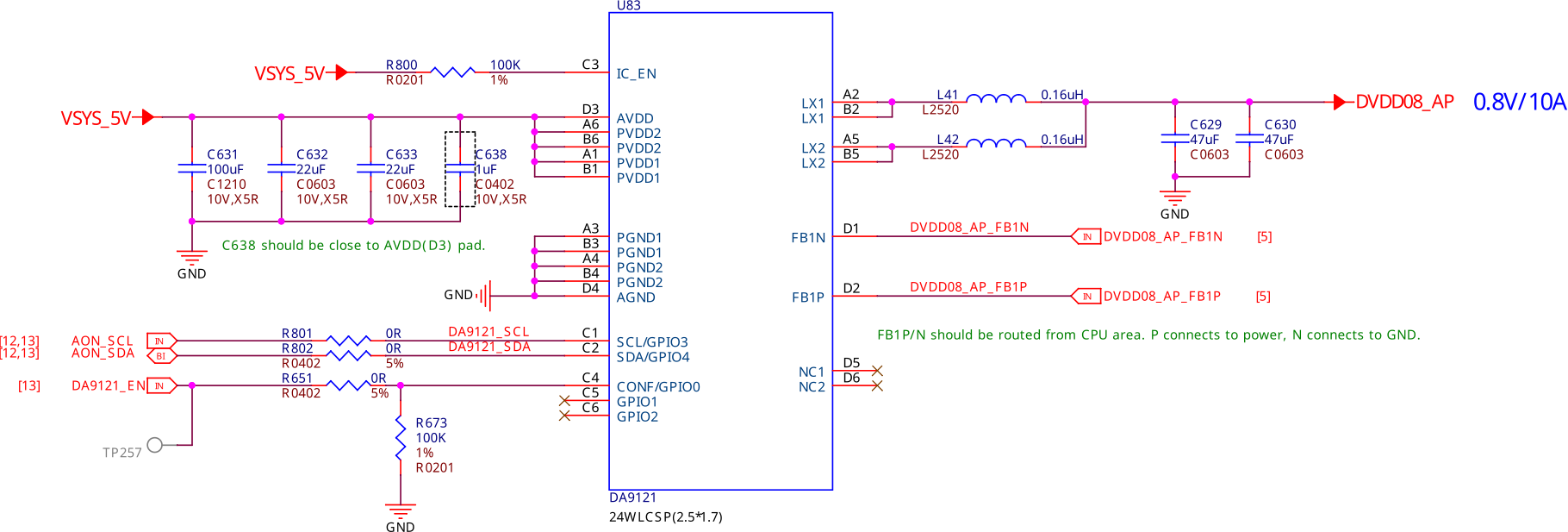

0.8V DCDC buck#

Fig. 521 0.8V DCDC buck converter#

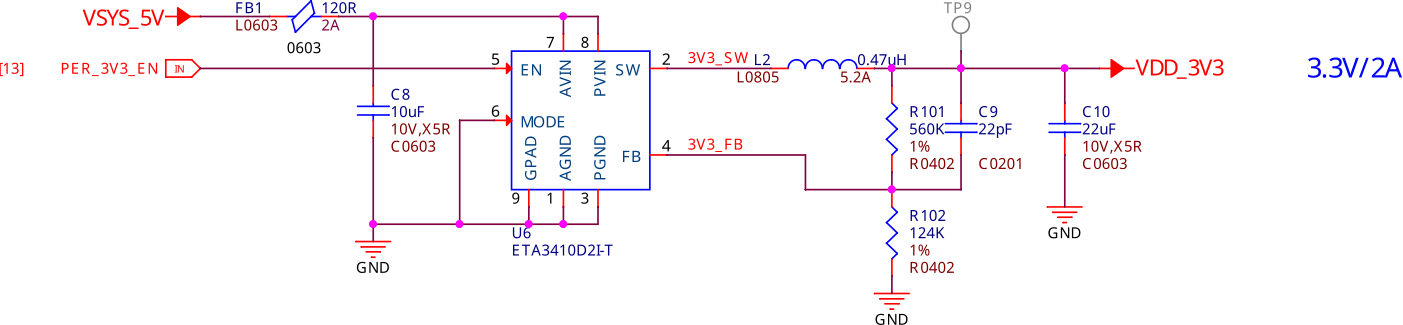

3.3V DCDC buck#

Fig. 522 3.3V DCDC buck converter#

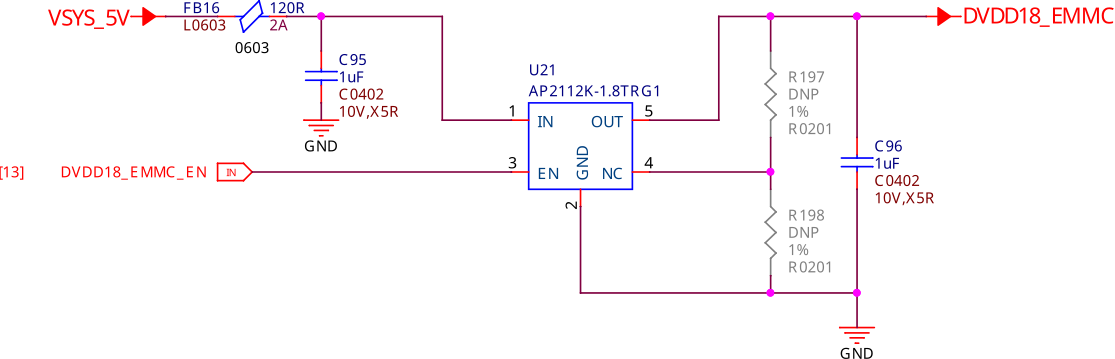

1.8V LDO#

Fig. 523 1.8V LDO regulator#

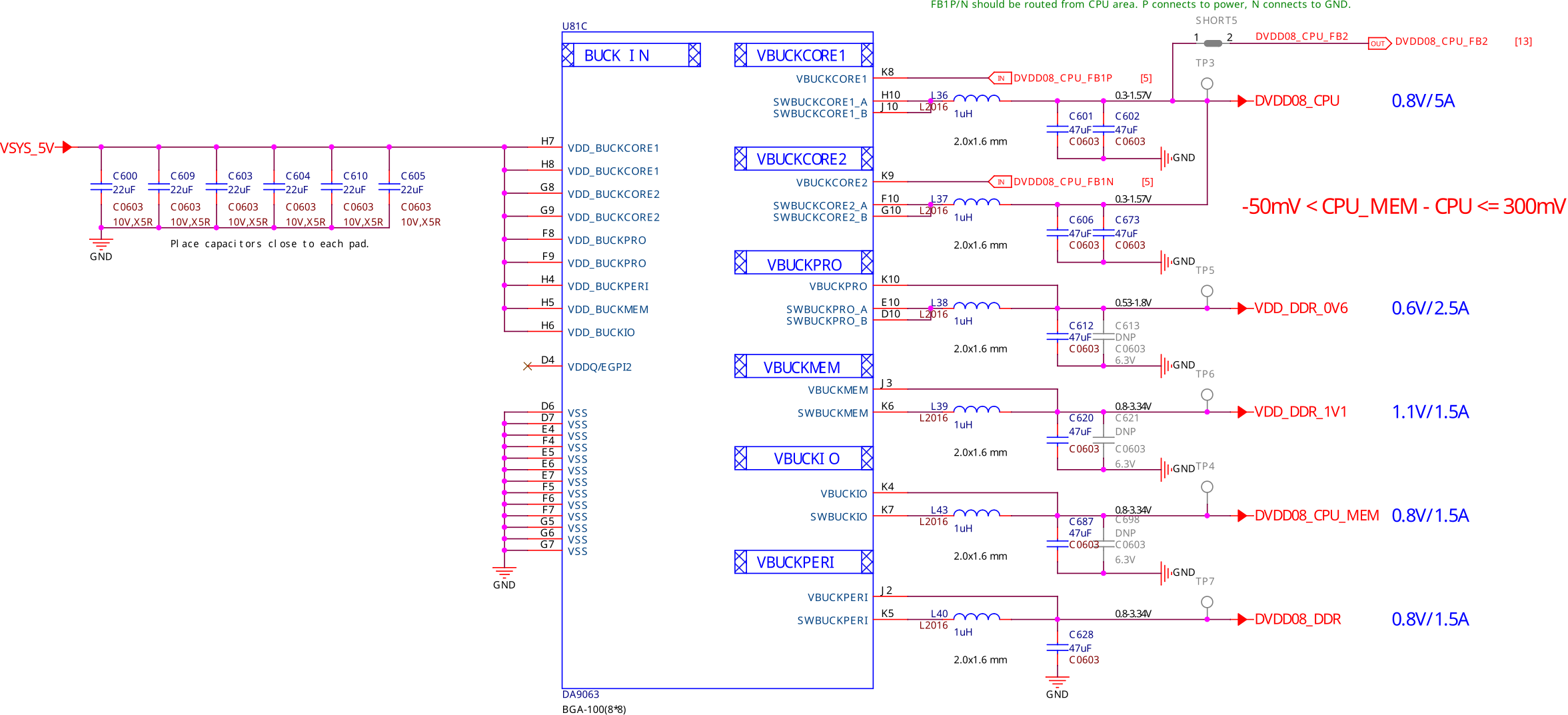

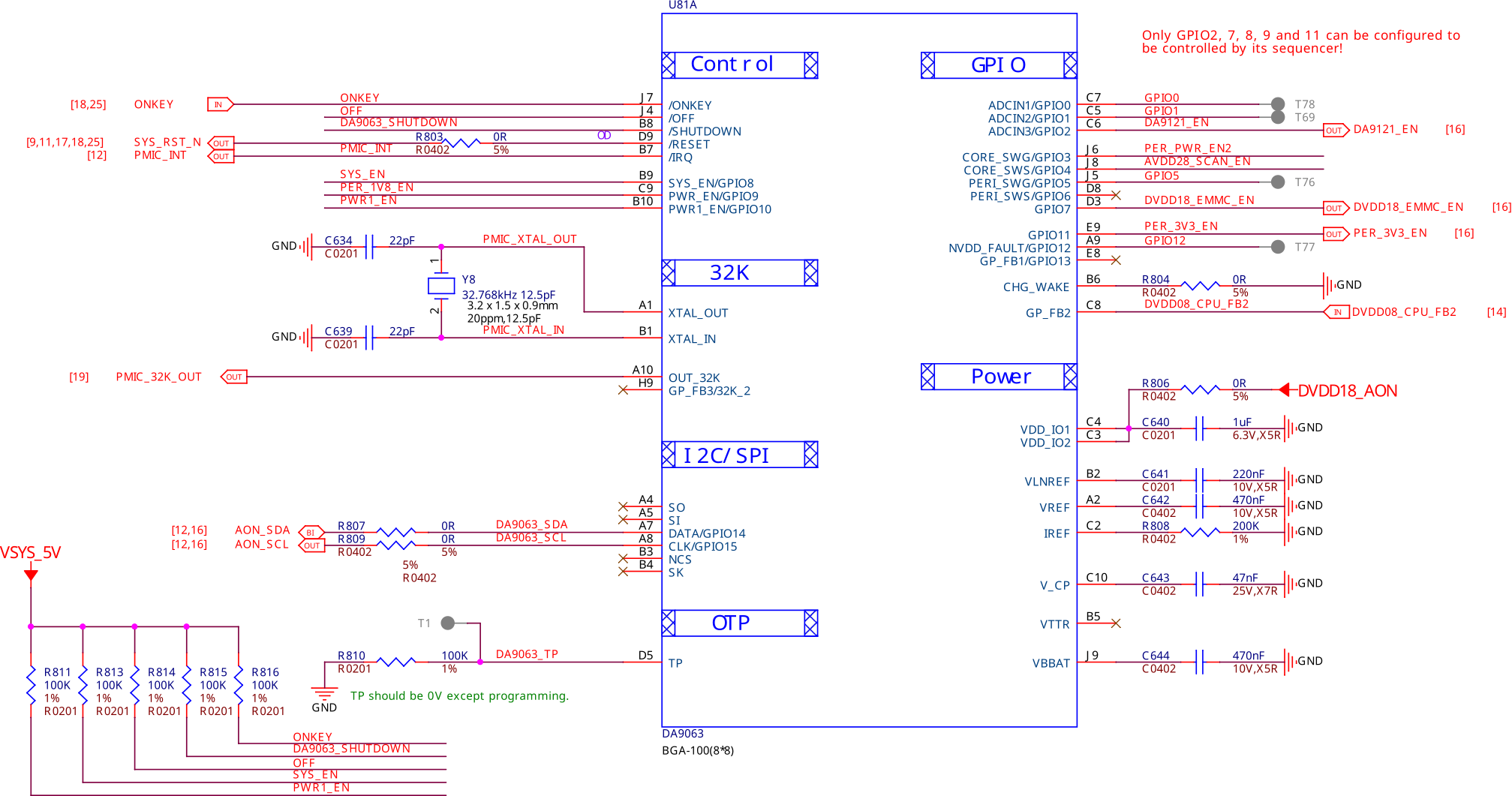

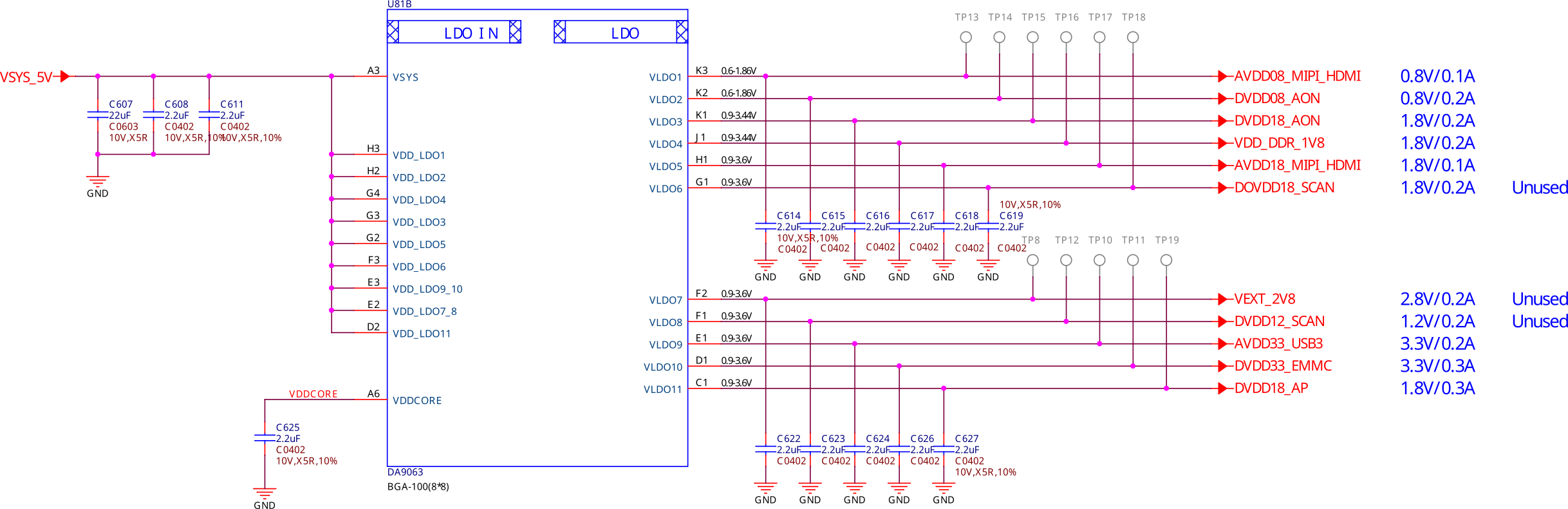

PMIC#

Fig. 524 PMIC Buck#

Fig. 525 PMIC Control#

Fig. 526 PMIC LDO#

General Connectivity and Expansion#

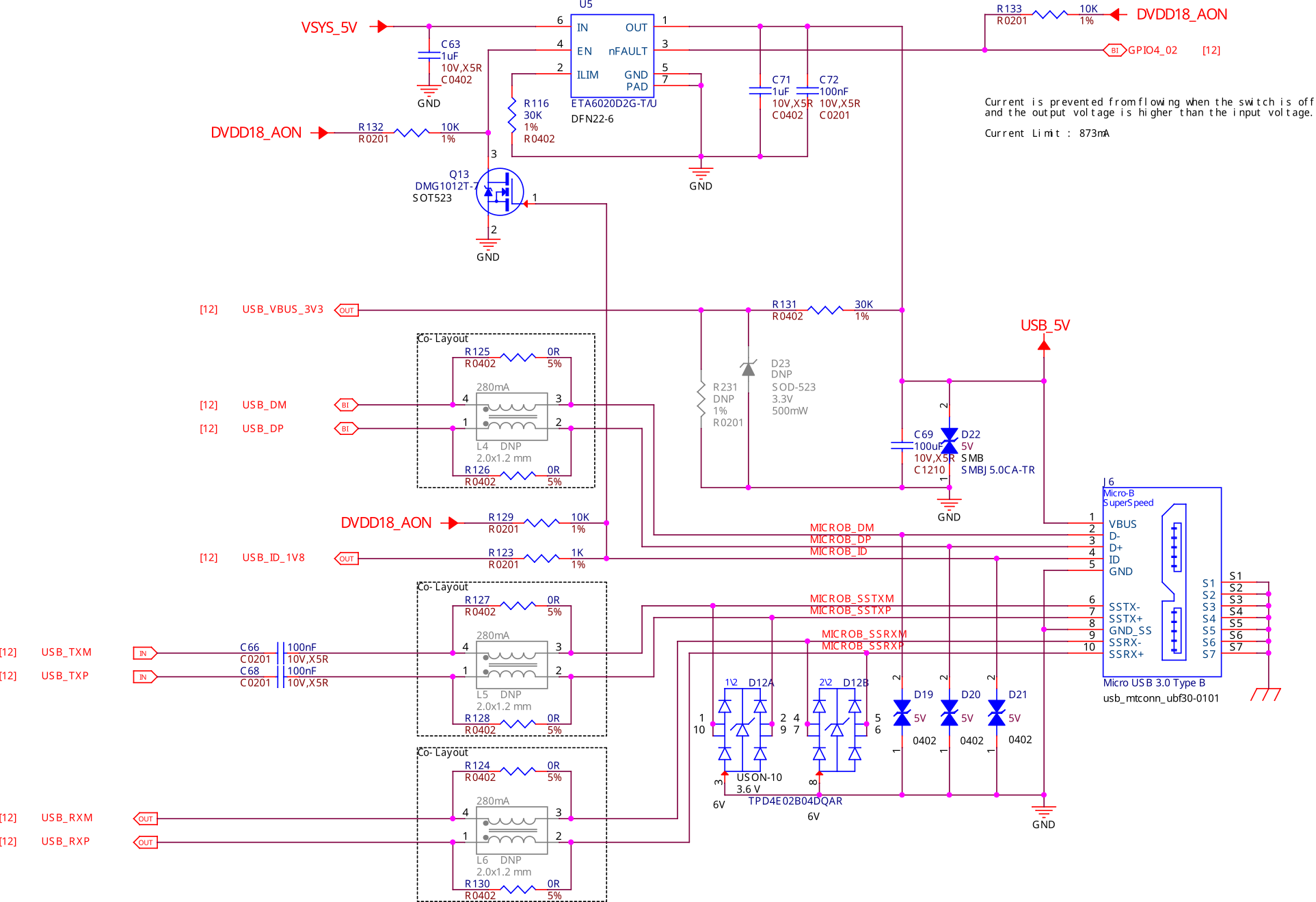

microUSB 3.0 port#

Fig. 527 microUSB 3.0 port#

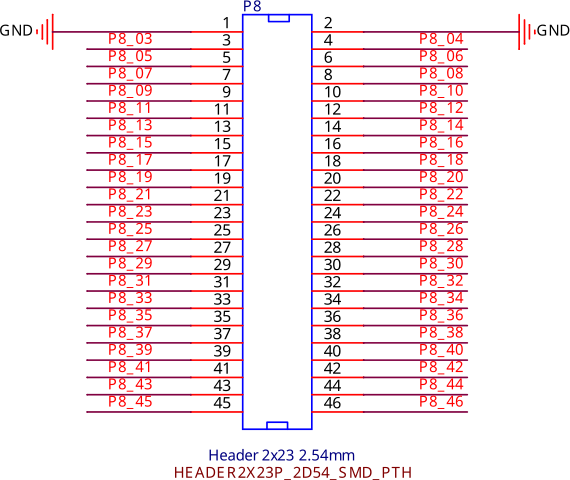

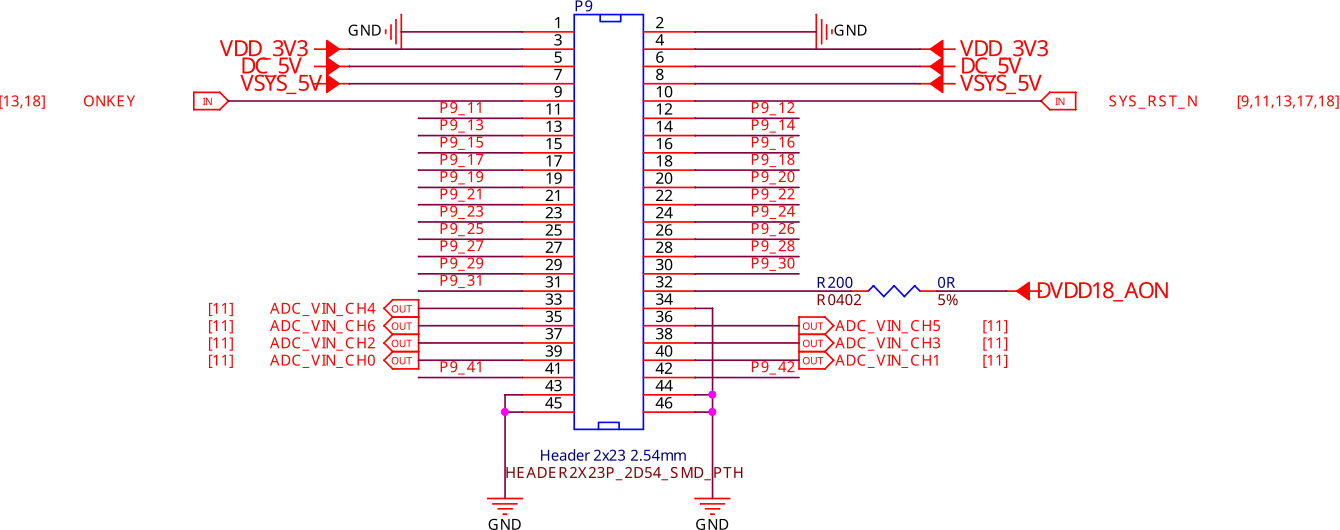

P8 & P9 cape header pins#

Fig. 528 P8 cape header#

Fig. 529 P9 cape header#

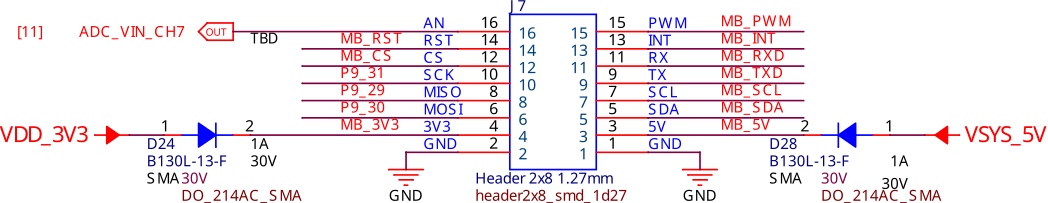

mikroBUS shuttle connector#

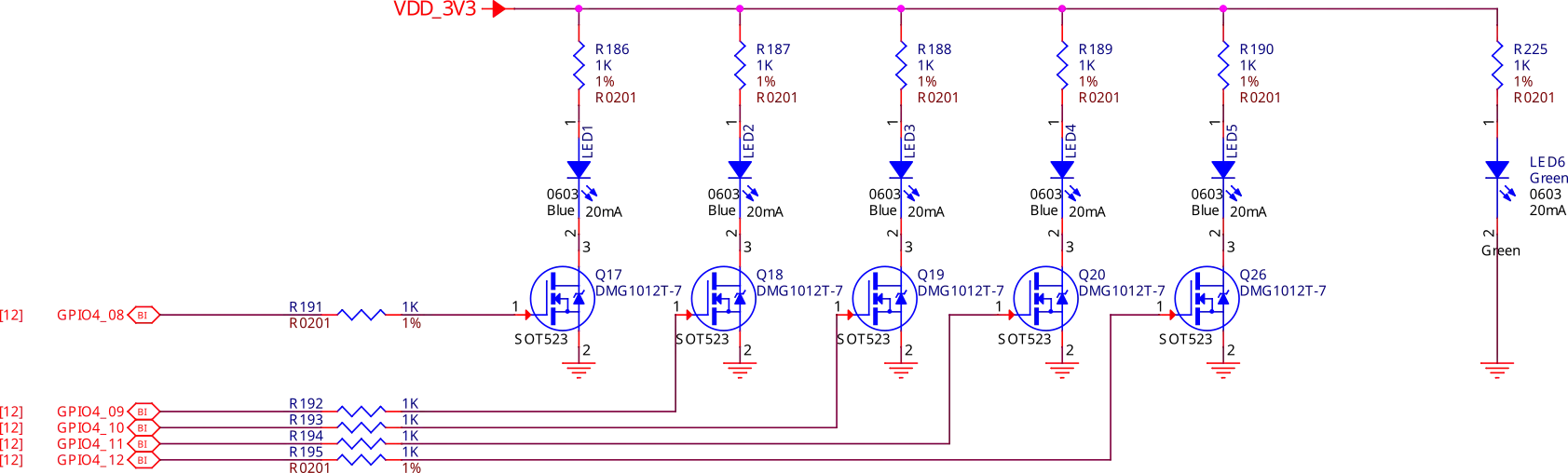

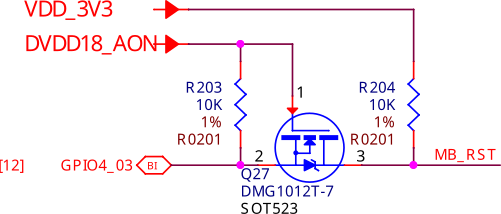

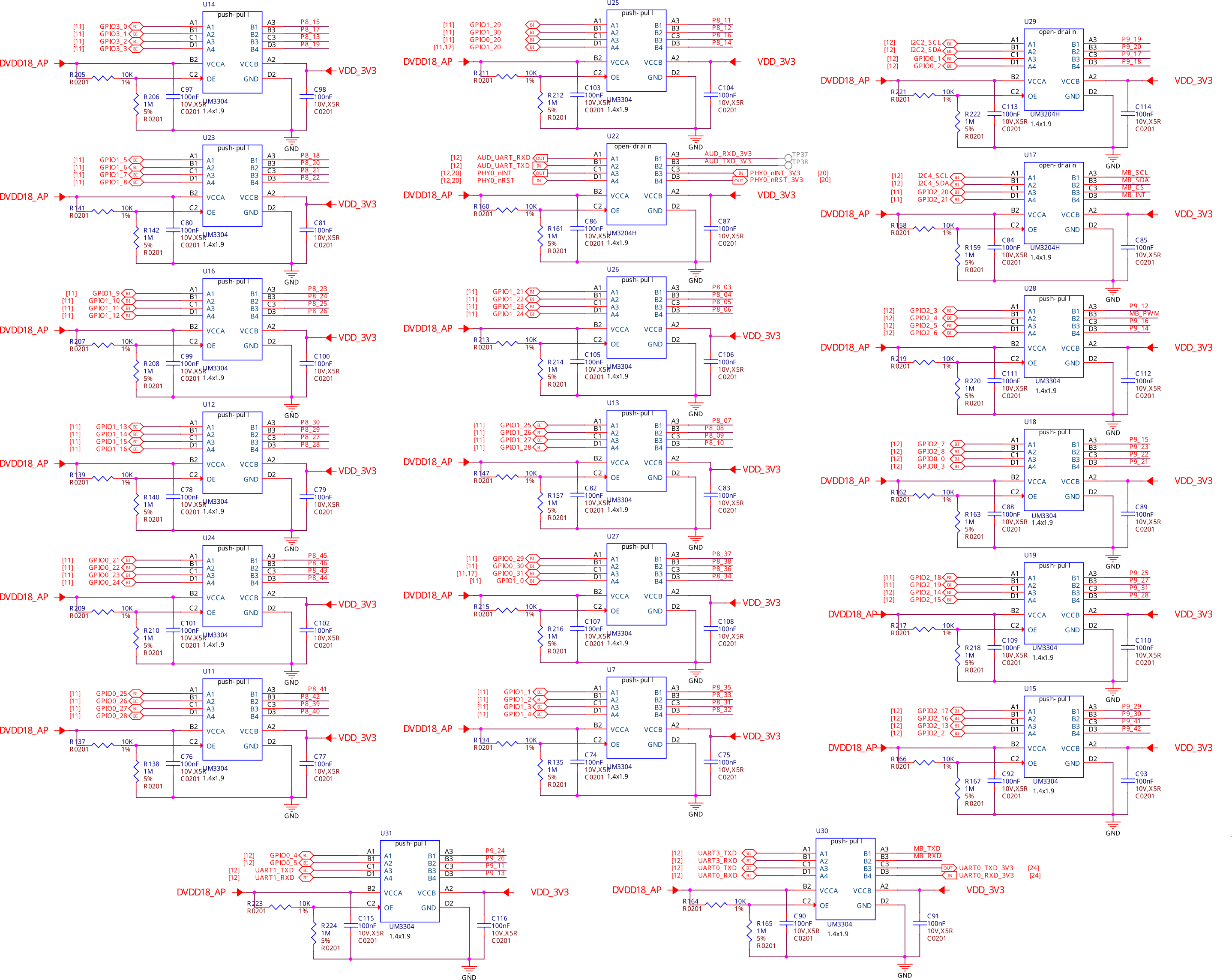

P8, P9, and mikroBUS helper circuitry#

Fig. 530 P8, P9, and mikroBUS level shifters#

Wired and wireless connectivity#

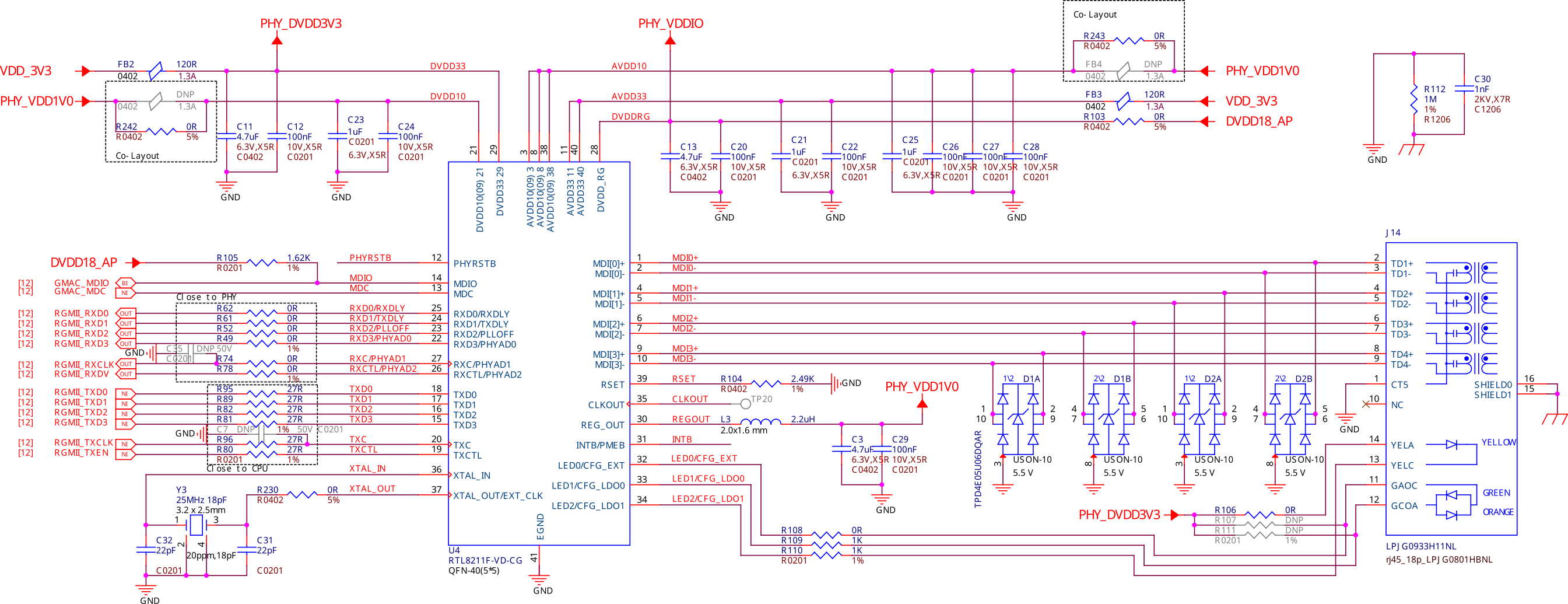

Ethernet#

Fig. 534 Ethernet#

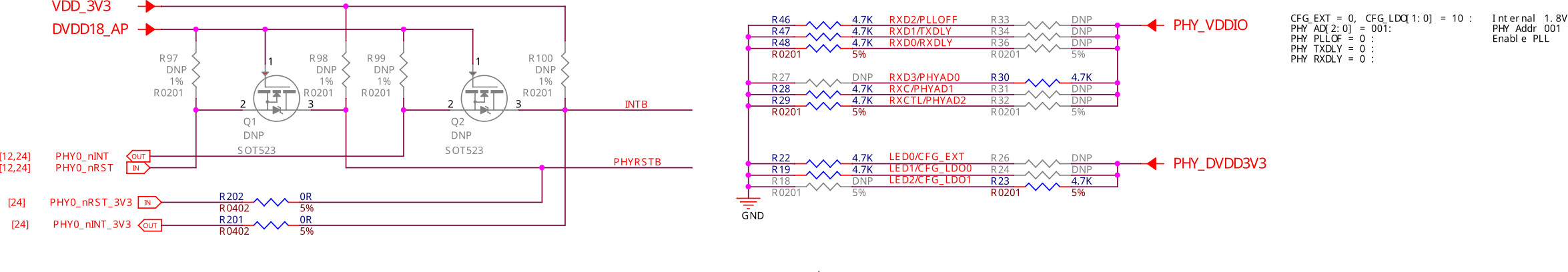

Fig. 535 Ethernet LevelShifter and Strapping#

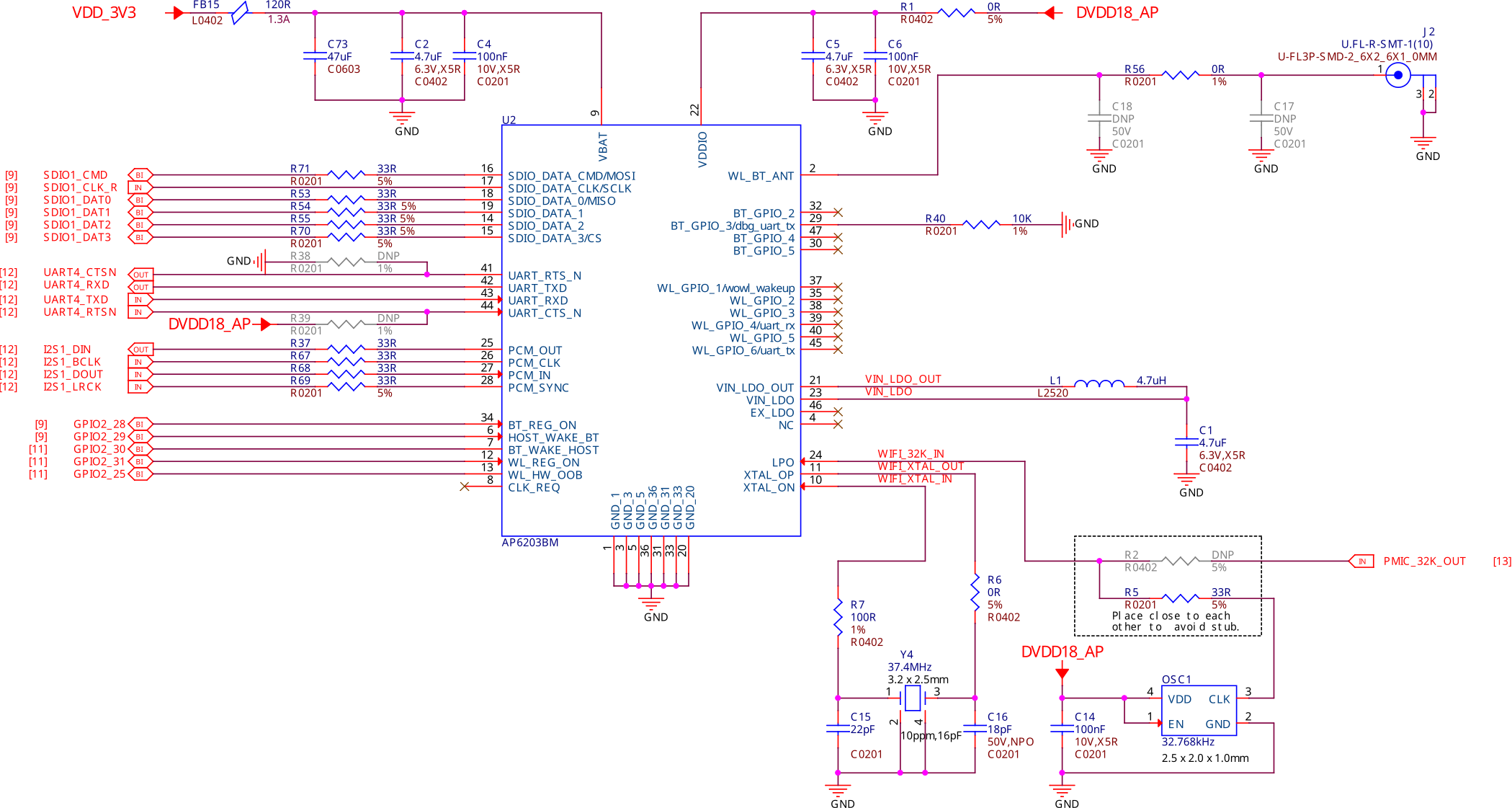

WiFi & Bluetooth#

Fig. 536 WiFi and Bluetooth#

Memory, Media and Data storage#

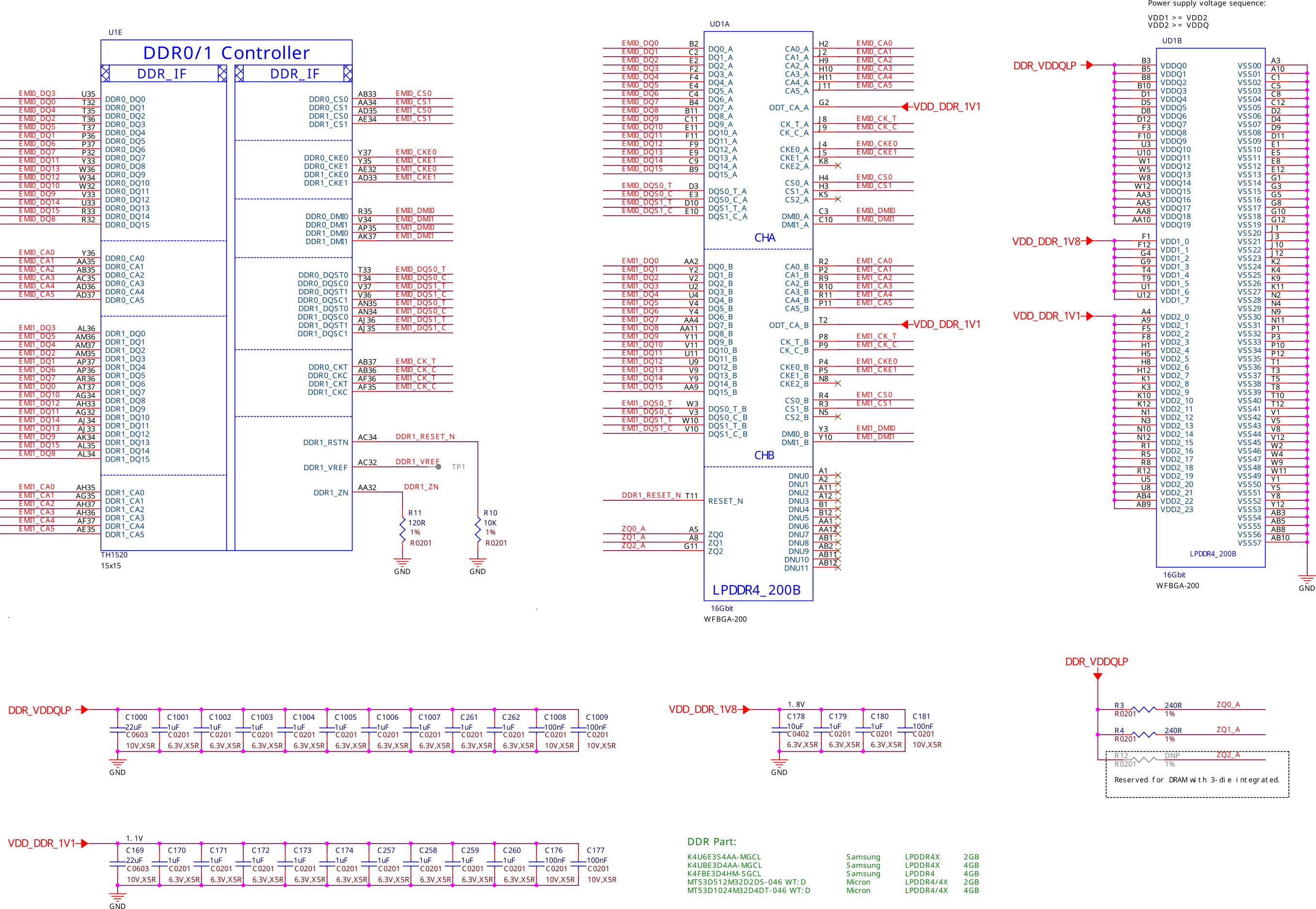

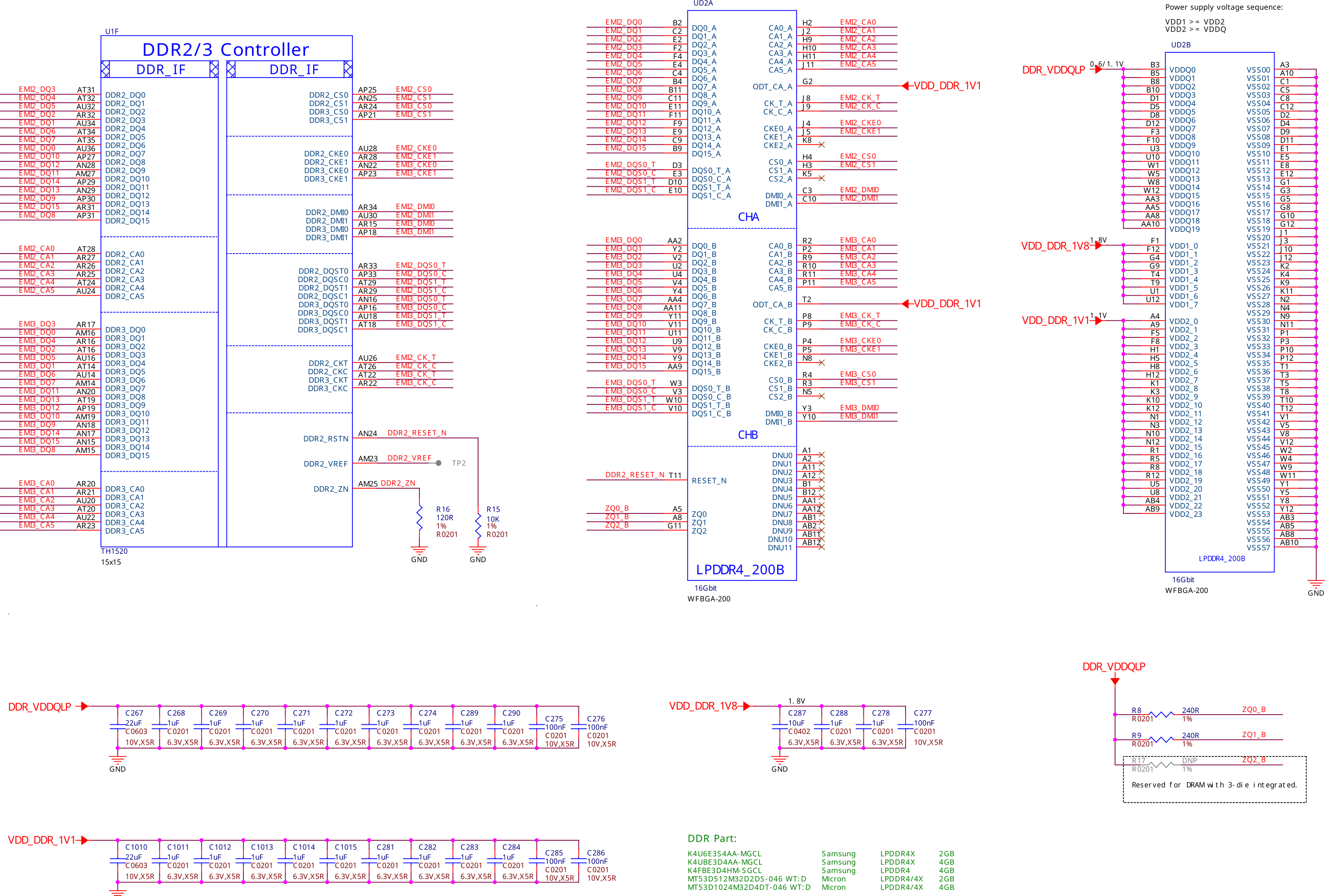

DDR memory#

Fig. 537 2GB DDR4 Memory chip1#

Fig. 538 2GB DDR4 Memory chip2#

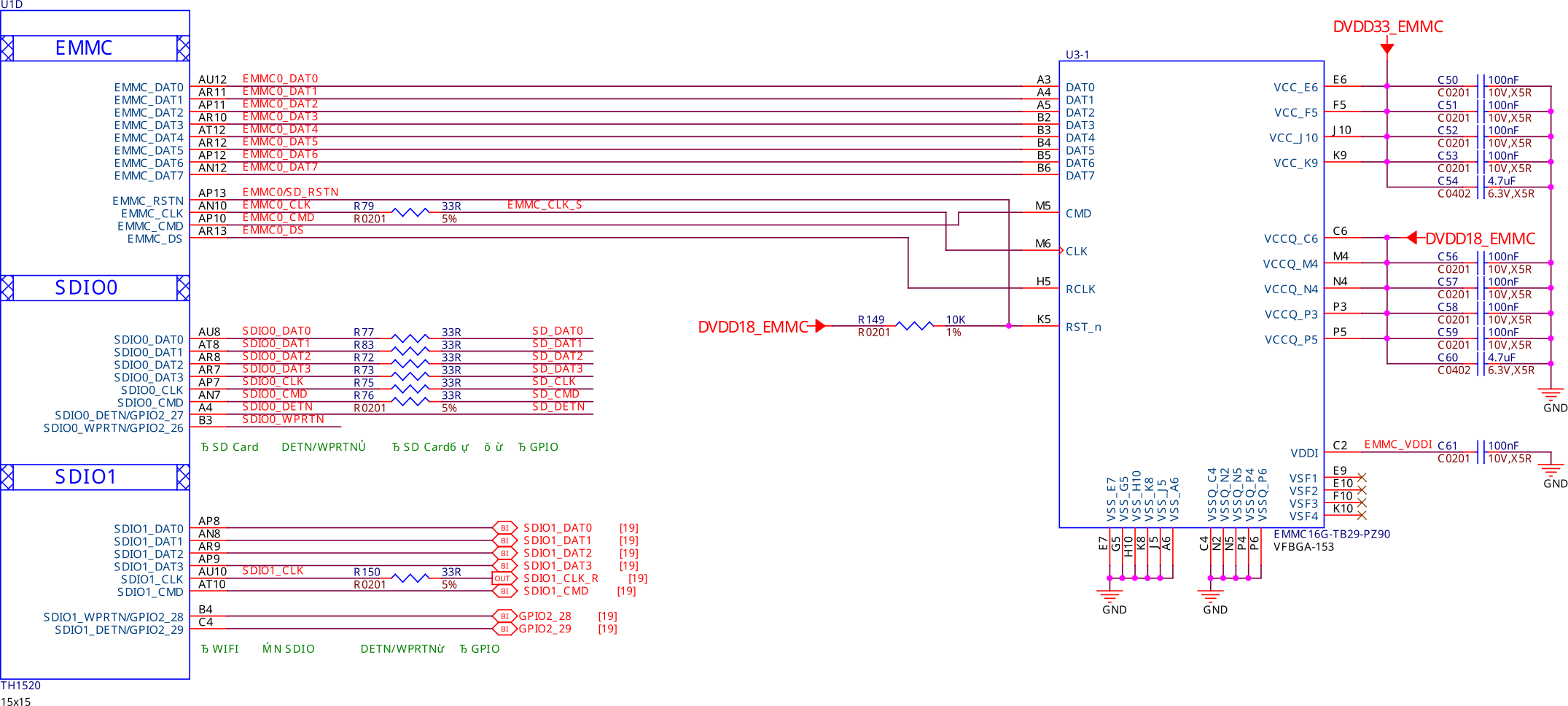

eMMC#

Fig. 539 16GB eMMC#

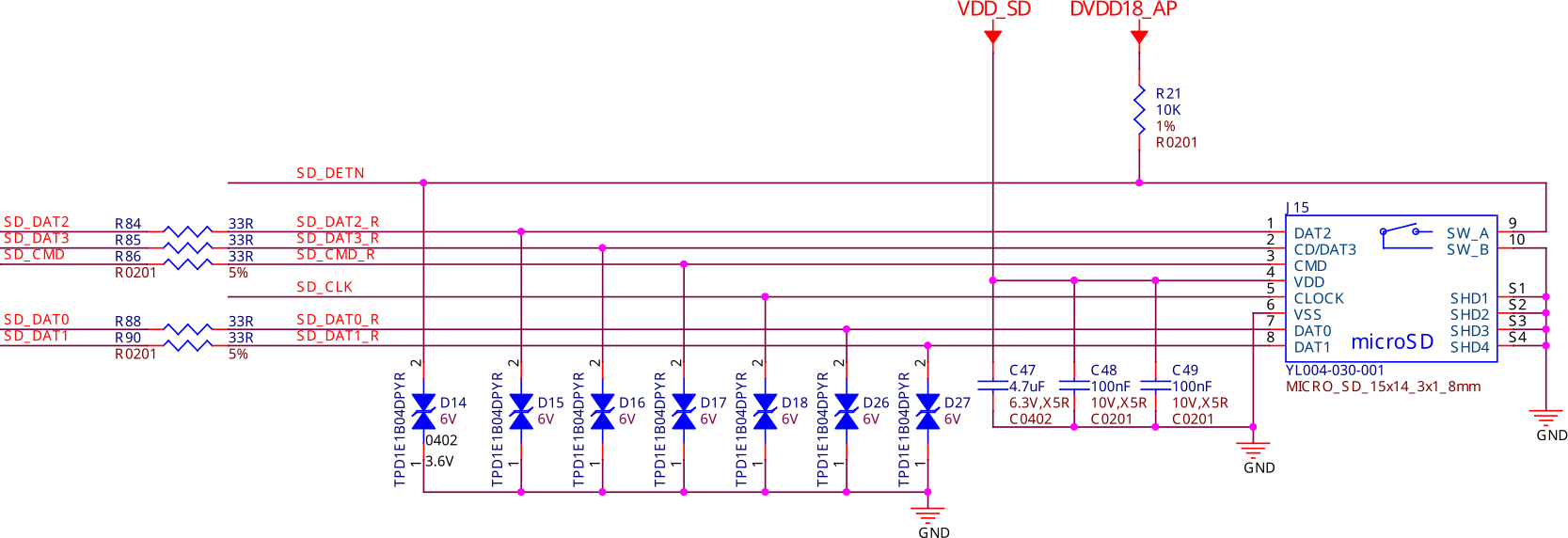

microSD#

Fig. 540 microSD card connector#

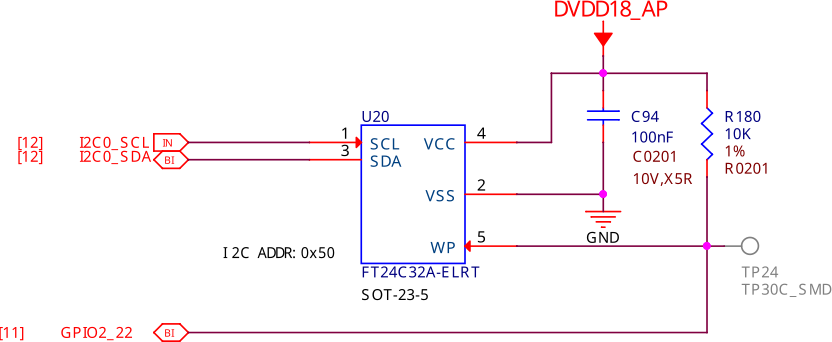

EEPROM#

Fig. 541 16GB EEPROM#

Multimedia I/O#

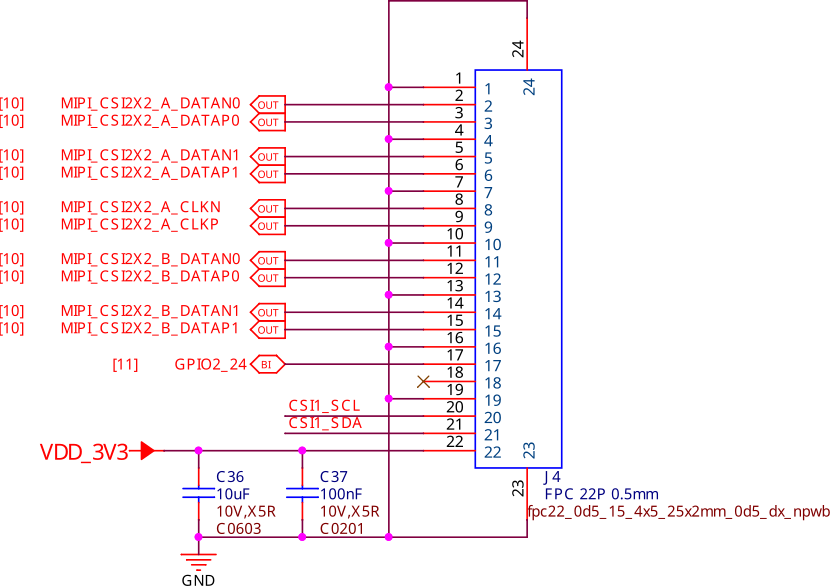

CSI0#

Fig. 542 CSI0 camera interface#

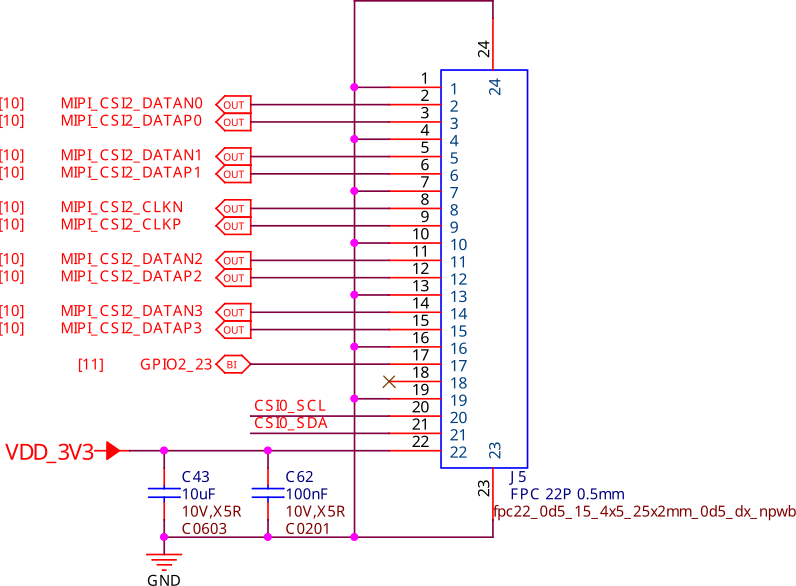

CSI1#

Fig. 543 CSI1 camera interface#

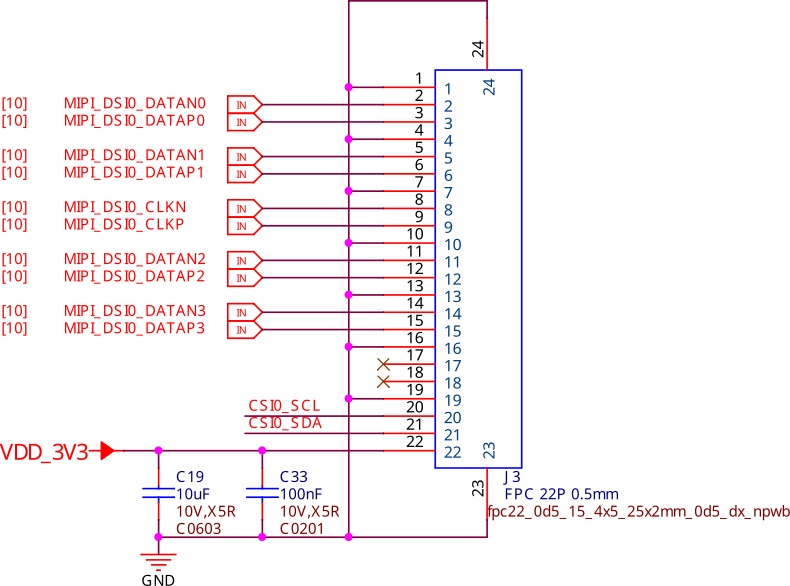

DSI#

Fig. 544 DSI display interface#

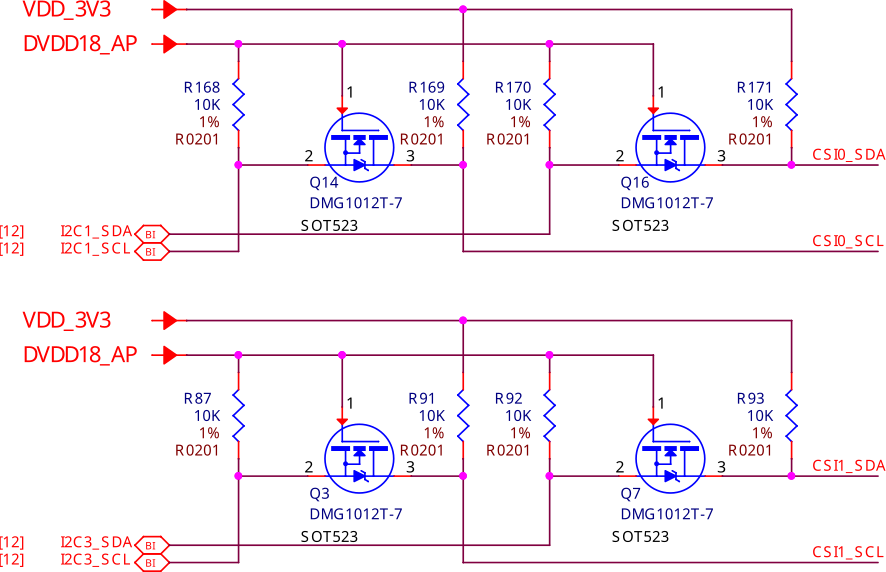

CSI & DSI level shifter#

Fig. 545 CSI & DSI level shifter#

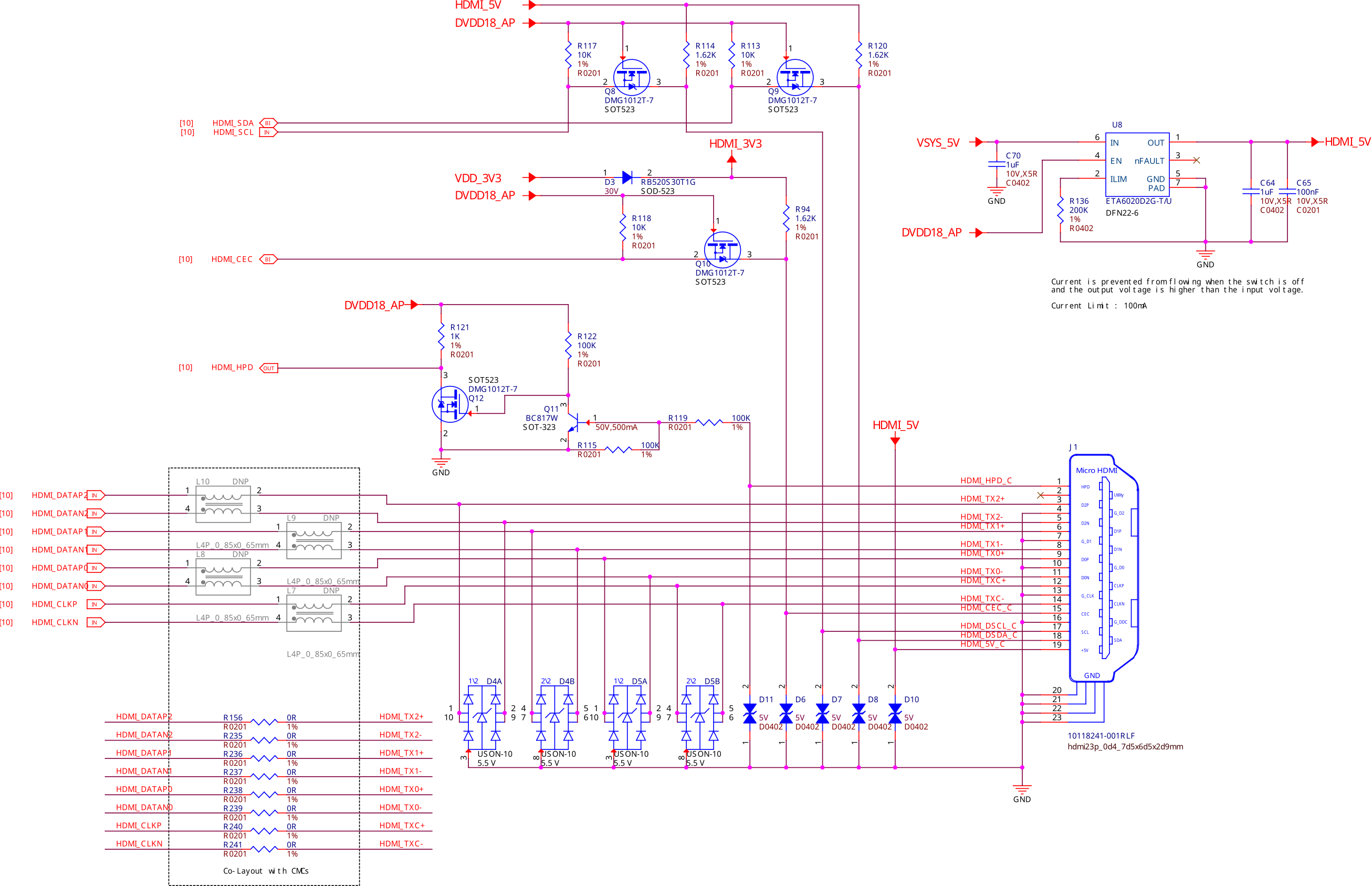

HDMI#

Fig. 546 HDMI display interface#

Debug#

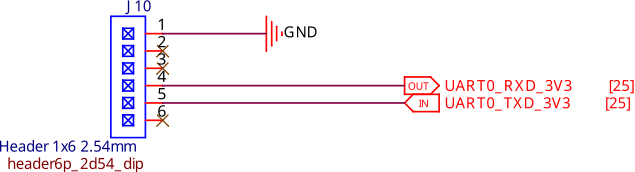

UART debug port#

Fig. 547 UART Debug port#

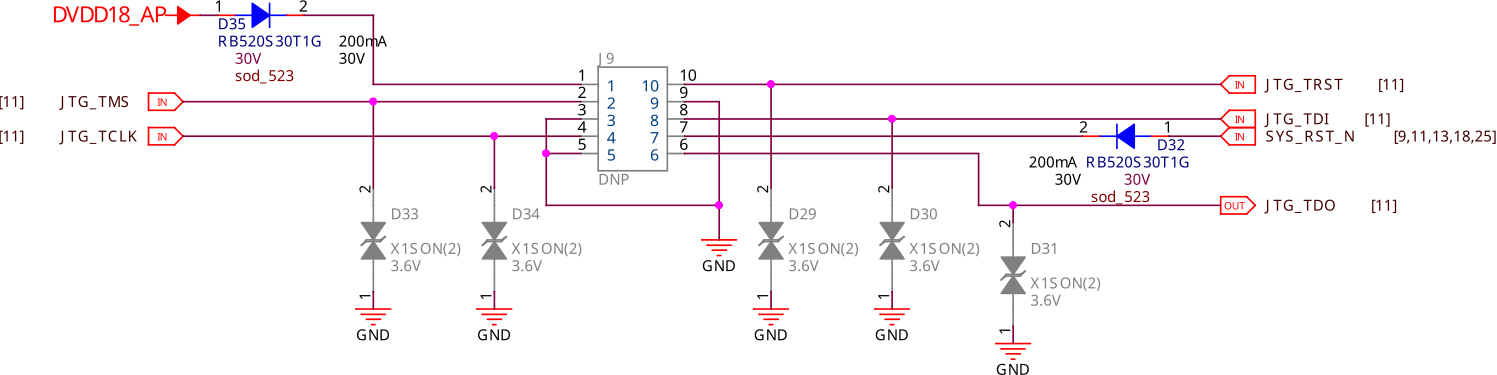

JTAG debug port#

Fig. 548 JTAG debug port#

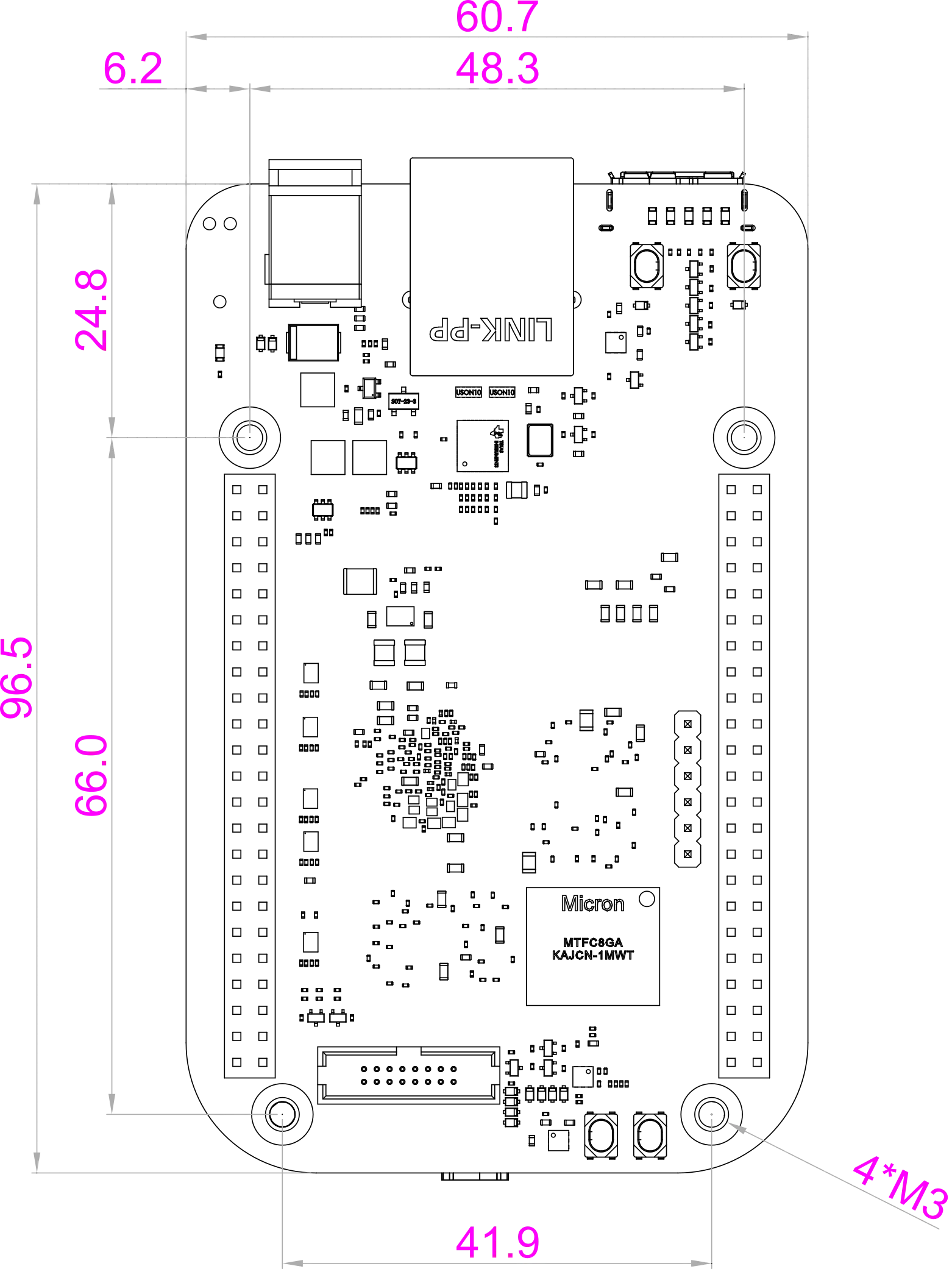

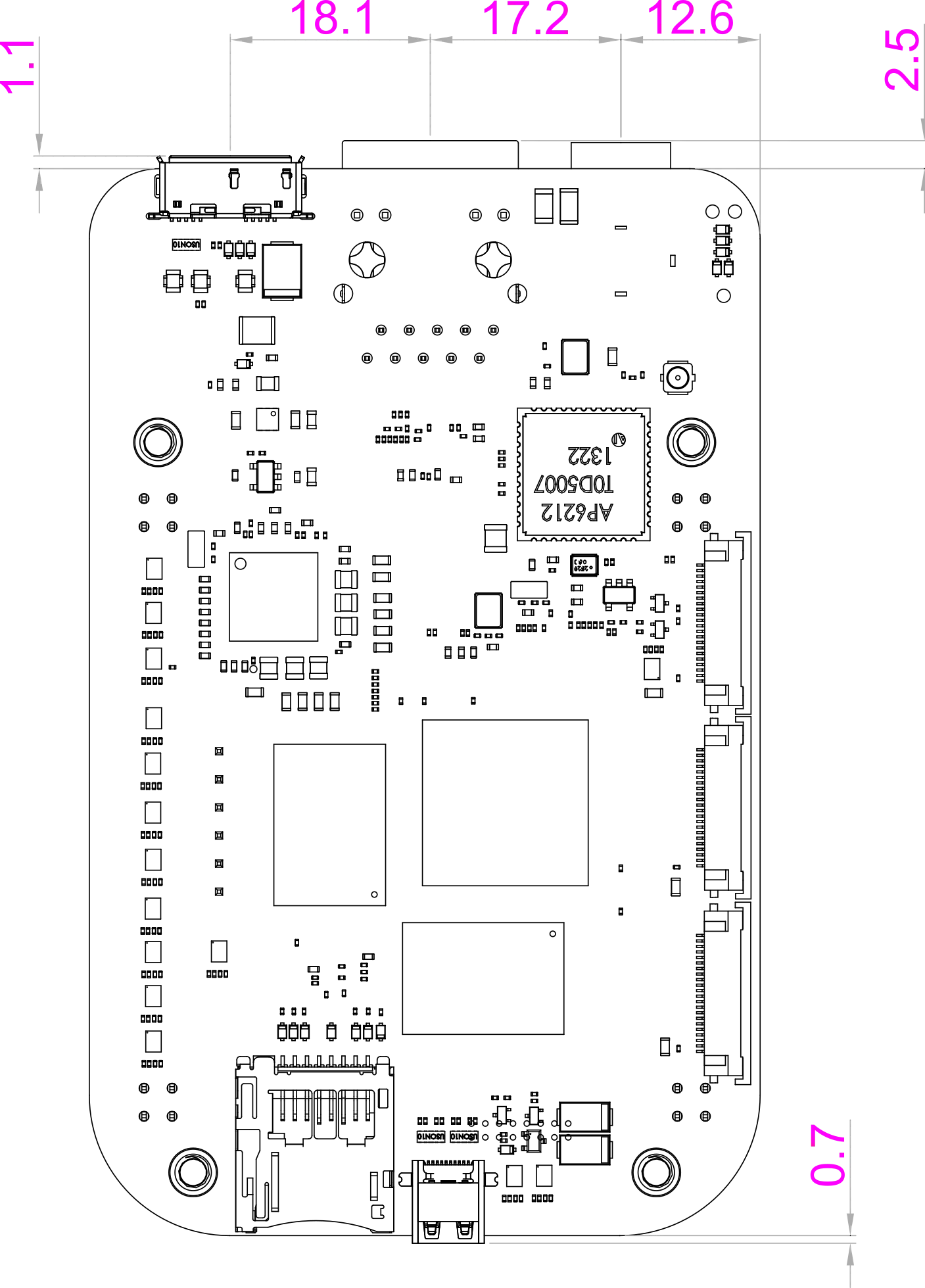

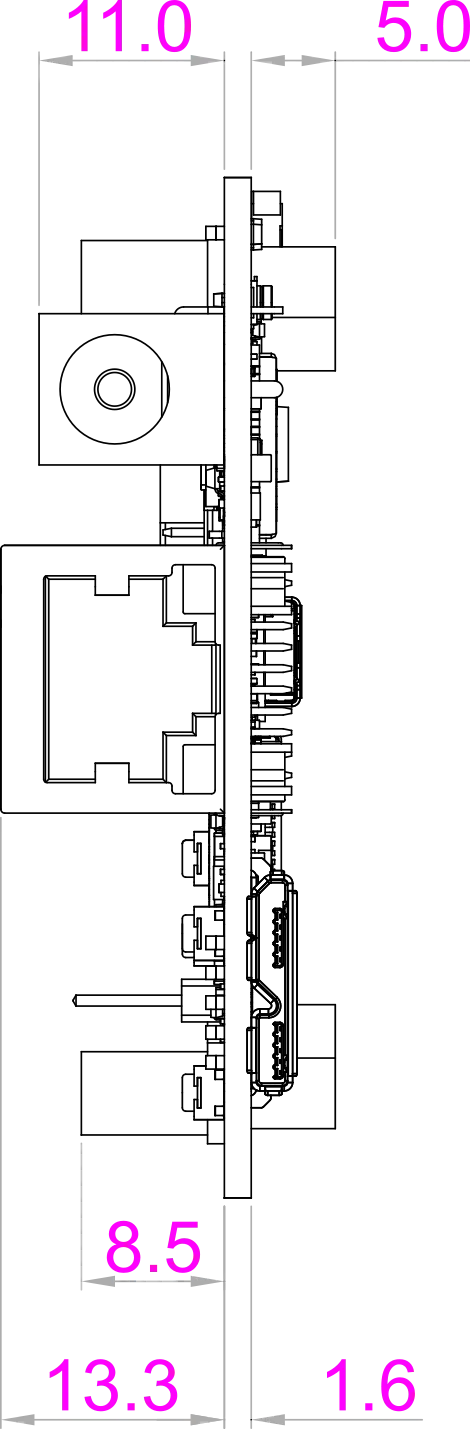

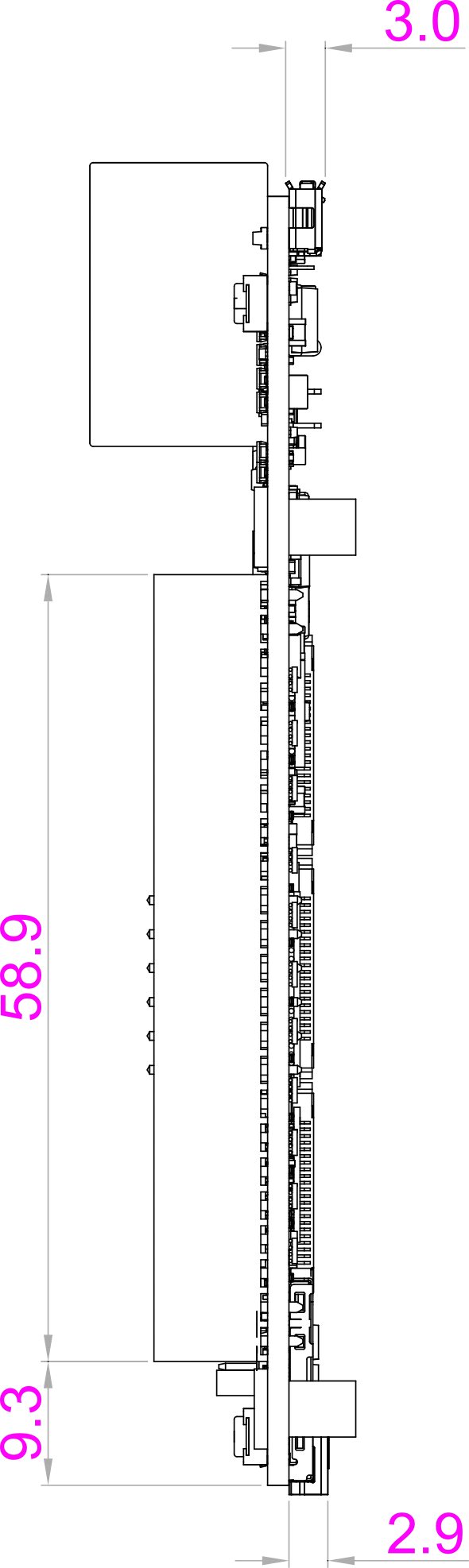

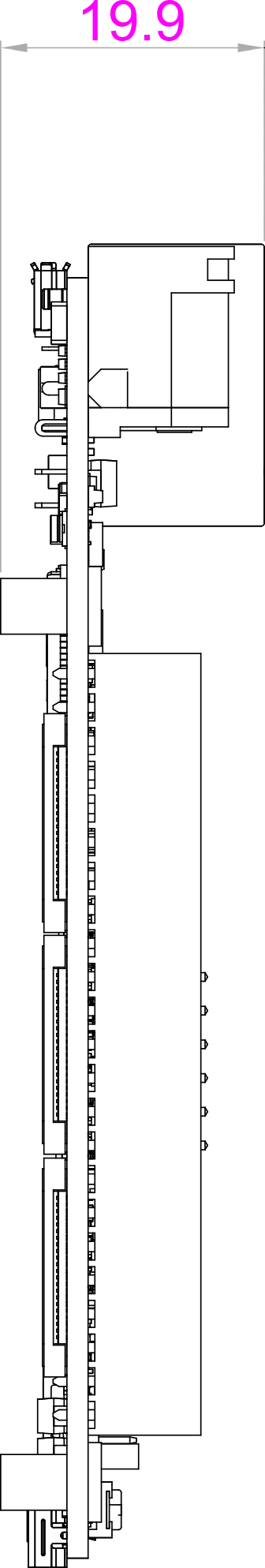

Mechanical Specifications#

Parameter |

Values |

|---|---|

Size |

96.5x60.7x19.9mm |

Max height |

21.1mm |

PCB Size |

96.5x60.5x1.6mm |

PCB Layers |

10 layers |

PCB Thickness |

1.6mm |

RoHS compliant |

yes |

Gross Weight |

128.8g |

Net weight |

49.7g |